# **IX4352NE**

# 9A Low Side SiC MOSFET & IGBT Driver

- Separate 9A peak source and sink outputs

- Operating Voltage Range: V<sub>DD</sub>-V<sub>SS</sub> up to 35V

- Internal charge pump regulator for selectable negative gate drive bias

- Desaturation detection with soft shutdown sink driver

- TTL and CMOS compatible input

- Under Voltage lockout (UVLO)

- Thermal shutdown

- Open drain FAULT output

### **Applications**

- On-board charger

- DC-DC converter

- Electric vehicle charging station

- Motor controller

- Power Inverter

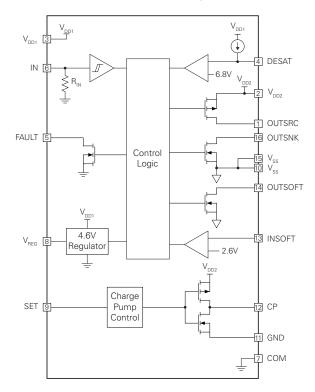

### **IX4352NE Functional Block Diagram**

### **Description**

The IX4352NE gate driver is designed specifically to drive SiC MOSFETs and high power IGBTs. Separate 9A source and sink outputs allow for tailored turn-on and turn-off timing while minimizing switching losses. An internal negative charge regulator provides a user-selectable negative gate drive bias for improved dV/dt immunity and faster turn-off.

Desaturation detection circuitry senses an over current condition of the SiC MOSFET and initiates a soft turn off, thus preventing a potentially damaging dV/dt event. The non-inverting logic input, IN, is TTL and CMOS compatible; internal level shifters provide the necessary bias to accommodate negative gate drive bias voltages. Additional protection features include UVLO detection and thermal shutdown. An open drain FAULT output signals a fault condition to the microcontroller.

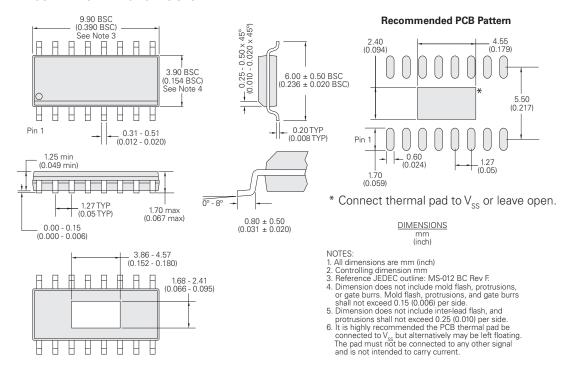

The IX4352NE is available in a thermally enhanced 16-pin narrow SOIC package.

#### **Ordering Information**

| Part       | Description                                                                 |

|------------|-----------------------------------------------------------------------------|

| IX4352NE   | 16-Pin narrow SOIC with exposed bottom side pad. In tubes (50/Tube)         |

| IX4352NETR | 16-Pin narrow SOIC with exposed bottom side pad. In Tape & Reel (2000/Reel) |

| 1. Specifications                                         |    |

|-----------------------------------------------------------|----|

| 1.1 Package Pinout                                        |    |

| 1.2 Pin Description                                       |    |

| 1.3 Absolute Maximum Ratings                              |    |

| 1.4 Recommended Operating Conditions                      |    |

| 1.5 Electrical Characteristics                            |    |

| 1.6 Thermal Characteristics                               |    |

| 1.7 Timing Diagram                                        |    |

|                                                           |    |

| 2. Performance Data                                       |    |

| 2 Functional Description                                  | 11 |

| <b>3. Functional Description</b>                          |    |

| • •                                                       |    |

| 3.2 Logic Input (IN)                                      |    |

| 3.3 Gate Drive Outputs                                    |    |

| 3.4 Internal 4.6V Regulator (V <sub>REG</sub> )           |    |

| 3.5 Negative Supply Voltage (V <sub>SS</sub> ) Generation |    |

| 3.6 Desaturation Detection and Protection                 |    |

| 3.7 DESAT Input Component Selection                       |    |

| 3.8 DESAT Blanking Time Stretching                        |    |

| 3.9 Thermal Shutdown                                      |    |

| 3.10 FAULT Output                                         |    |

|                                                           |    |

| 4. Manufacturing Information                              |    |

| 4.1 Moisture Sensitivity                                  |    |

| 4.2 ESD Sensitivity                                       |    |

| 4.3 Soldering Profile                                     |    |

| 4.4 Board Wash                                            |    |

| 4.5 Mechanical Dimensions                                 | 16 |

# 1 Specifications

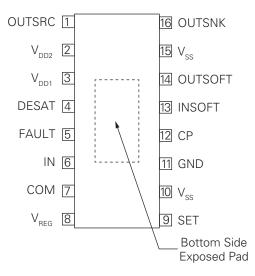

# 1.1 Package Pinout

## 1.2 Pin Description

| Pin    | Name             | Pin Type | Description                                                                                                                                                          |

|--------|------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | OUTSRC           | Output   | Gate driver, source.                                                                                                                                                 |

| 2      | $V_{DD2}$        | Power    | Positive supply voltage for driver and charge pump outputs. Connect to pin 3 ( $V_{DD1}$ ).                                                                          |

| 3      | V <sub>DD1</sub> | Power    | Positive supply voltage for logic and control circuits. Connect to pin 2 (V <sub>DD2</sub> ).                                                                        |

| 4      | DESAT            | Input    | Sense input for desaturation detection.                                                                                                                              |

| 5      | FAULT            | Output   | Fault status, Open-Drain, active low.                                                                                                                                |

| 6      | IN               | Input    | Logic input.                                                                                                                                                         |

| 7      | COM              | Power    | Common ground connection. Connect to GND.                                                                                                                            |

| 8      | $V_{REG}$        | Output   | 4.6V regulator output.                                                                                                                                               |

| 9      | SET              | Input    | Charge pump control.                                                                                                                                                 |

| 10, 15 | $V_{SS}$         | Power    | Negative supply voltage. Connect pin 10 to pin 15 on the PCB.                                                                                                        |

| 11     | GND              | Power    | Charge pump ground connection. Connect to COM.                                                                                                                       |

| 12     | СР               | Output   | Charge pump output.                                                                                                                                                  |

| 13     | INSOFT           | Input    | Soft Shutdown sense input.                                                                                                                                           |

| 14     | OUTSOFT          | Output   | Gate driver, Soft Shutdown sink.                                                                                                                                     |

| 16     | OUTSNK           | Output   | Gate driver, sink.                                                                                                                                                   |

| -      | Exposed Pad      | Thermal  | It is highly recommended the exposed pad be connected to $V_{SS}$ . Alternatively, it may be allowed to float, but must not be connected to any other signal or net. |

### 1.3 Absolute Maximum Ratings

Absolute Maximum Ratings are stress ratings. Stresses in excess of these ratings can cause permanent damage to the device. Functional operation of the device at conditions beyond those indicated in the operational sections of this data sheet is not implied.

Unless otherwise specified all voltages are with respect to COM, electrical ratings are over the operational ambient temperature range, and  $V_{DD} = V_{DD1}$  connected to  $V_{DD2}$ .

| Downwater                 | Counch of                                                        | Va                    | Value                  |                  |  |

|---------------------------|------------------------------------------------------------------|-----------------------|------------------------|------------------|--|

| Parameter                 | Symbol                                                           | Minimum               | Maximum                | Units            |  |

| Positive Supply Voltage   | $V_{DD}$                                                         | -0.3                  | 32                     | V                |  |

| Negative Supply Voltage   | V <sub>SS</sub>                                                  | V <sub>DD</sub> - 40  | 0.5 1                  | V                |  |

| Supply Voltage Range      | $V_{DD}$ - $V_{SS}$                                              | -0.3                  | 40                     | V                |  |

| Ground Separation         | $V_{GND}$                                                        | -0.3                  | +0.3                   | V                |  |

| Gate Drive Output Voltage | V <sub>OUTSRC</sub> , V <sub>OUTSNK</sub> , V <sub>OUTSOFT</sub> | V <sub>SS</sub> - 0.3 | $V_{DD2} + 0.3$        | V                |  |

|                           | loutsrc , loutsnk                                                | -                     | ±9                     | ۸_               |  |

| Gate Drive Output Current | loutsoft                                                         | -                     | 1                      | - A <sub>P</sub> |  |

| IN Input Voltage          | V <sub>IN</sub>                                                  | -0.3                  | 7                      | V                |  |

| DESAT Input Voltage       | V <sub>DESAT</sub>                                               | -0.3                  | V <sub>DD1</sub> + 0.3 | V                |  |

| SET Input Voltage         | V <sub>SET</sub>                                                 | - 1                   | 7                      | V                |  |

| FAULT Output Voltage      | V <sub>FAULT</sub>                                               | -0.3                  | V <sub>DD1</sub> + 0.3 | V                |  |

| Regulator Output Voltage  | V <sub>REG</sub>                                                 | -0.3                  | 7                      | V                |  |

| Junction Temperature      | TJ                                                               | -55                   | +150                   | °C               |  |

| Storage Temperature       | T <sub>STG</sub>                                                 | -55                   | +150                   | °C               |  |

$<sup>^{1}</sup>$  The current into  $V_{SS}$  must never exceed 1mA.

### 1.4 Recommended Operating Conditions

| Parameter                                                                      | Symbol          | Va      | Units   |        |

|--------------------------------------------------------------------------------|-----------------|---------|---------|--------|

| rarameter                                                                      | Symbol          | Minimum | Maximum | Ullits |

| Positive Supply Voltage (V <sub>DD1</sub> =V <sub>DD2</sub> =V <sub>DD</sub> ) | $V_{DD}$        | 13      | 25      | V      |

| Negative Supply Voltage                                                        | $V_{SS}$        | -3.5    | -10     | V      |

| Input Voltage                                                                  | V <sub>IN</sub> | 0       | 5.5     | V      |

| Operating Ambient Temperature                                                  | T <sub>A</sub>  | -40     | 125     | °C     |

#### 1.5 Electrical Characteristics

Typical values are characteristic of the device at  $T_A=25^{\circ}$ C and are the result of engineering evaluations. They are provided for informational purposes only and are not part of the manufacturing testing requirements.

Unless otherwise specified, all voltages are referenced to COM, electrical characteristics are guaranteed at:  $V_{DD1} = V_{DD2} = V_{DD} = 20V$ ,  $V_{SS} = -5V$ ,  $V_{GND} = 0V$ ,  $V_{INH} = 5V$ ,  $V_{INL} = 0V$ ,  $C_{DD} = C_{REG} = 4.7 \mu F$ ,  $C_{SS} = 10 \mu F$ , and  $-40^{\circ}C \le T_{A} \le +125^{\circ}C$ .

### 1.5.1 V<sub>DD</sub>

| Parameter                | Conditions                                               | Symbol                |         | Units   |         |        |

|--------------------------|----------------------------------------------------------|-----------------------|---------|---------|---------|--------|

| raidilietei              | Conditions                                               | Зуппоп                | Minimum | Typical | Maximum | Uiiits |

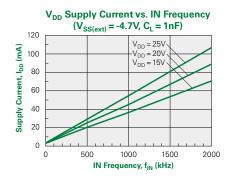

| Operating Supply Current | $f_{IN}$ =100kHz, $V_{SET}$ =0.4V, $C_{LOAD}$ =2.2nF     | I <sub>DD</sub>       | -       | 19      | -       | mA     |

| Quiescent Supply Current | V <sub>IN</sub> =0V, V <sub>SET</sub> =-0.4V,<br>No load | I <sub>DDQ</sub>      | -       | 2.9     | 4.4     | mA     |

| UVLO Rising Threshold    | V <sub>DD</sub> Rising                                   | $V_{DDUV\_th}$        | 10      | 12      | 13      | V      |

| UVLO Hysteresis          | V <sub>DD</sub> Falling                                  | V <sub>DDUV_hys</sub> | -       | 2       | -       | V      |

# 1.5.2 V<sub>REG</sub>

| Parameter                | Conditions                                              | Symbol           |         | Units   |         |        |

|--------------------------|---------------------------------------------------------|------------------|---------|---------|---------|--------|

| raiailletei              |                                                         |                  | Minimum | Typical | Maximum | Oilles |

| Regulator Output Voltage | I <sub>REG</sub> =-5mA                                  | V <sub>REG</sub> | 4.2     | 4.6     | 5       | V      |

| Line Regulation          | 15V < V <sub>DD</sub> < 25V,<br>I <sub>REG</sub> = -5mA | $\DeltaV_REG$    | -       | 0.1     | 0.2     | V      |

| Load Regulation          | -1mA≤I <sub>REG</sub> ≤ -10mA                           |                  | -       | 0.1     | 0.4     | V      |

### 1.5.3 Charge Pump and $V_{SS}$

| Parameter                       | Conditions                                 | Symbol                |         | Units   |         |        |

|---------------------------------|--------------------------------------------|-----------------------|---------|---------|---------|--------|

|                                 | Conditions                                 | Syllibol              | Minimum | Typical | Maximum | Ullits |

| UVLO Negative Threshold         | V <sub>SS</sub> Increasing                 | V <sub>SSUV_th-</sub> | -1      | -2.2    | -3.5    | V      |

| UVLO Positive Threshold         | V <sub>SS</sub> Decreasing                 | V <sub>SSUV_th+</sub> | -2      | -1.2    | -0.1    | V      |

| Average V <sub>SS</sub> Current | $C_{CP}=68nF, R_{CP}=33\Omega$             | I <sub>SS</sub>       | -       | -       | 50      | mA     |

| Charge Pump Frequency           | V <sub>SET</sub> =+0.4V                    | f <sub>OSC</sub>      | 90      | 125     | 160     | kHz    |

| Charge Pump Enable Threshold    | -                                          | V <sub>SET_th</sub>   | 30      | 110     | 250     | mV     |

| SET Input Leakage Current       | V <sub>SET</sub> =0V, V <sub>SET</sub> =5V | I <sub>SET</sub>      | -       | <10     | -       | nA     |

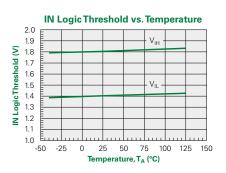

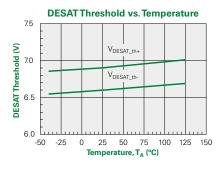

### 1.5.4 Desaturation

| Paramatar                      | Conditions             | Symbol                |         | Units   |         |        |

|--------------------------------|------------------------|-----------------------|---------|---------|---------|--------|

| Parameter                      |                        |                       | Minimum | Typical | Maximum | Ullits |

| DESAT Source Current           | V <sub>DESAT</sub> =0V | I <sub>DESAT</sub>    | 400     | 570     | 750     | μА     |

| DESAT Detect Threshold Voltage | -                      | V <sub>DESAT_th</sub> | 6       | 6.9     | 8       | V      |

| Blanking Time                  | $C_{BLANK} = 0\mu F$   | t <sub>BLANK</sub>    | -       | 250     | -       | ns     |

| DESAT Pull Down On-Resistance  | $V_{IN} = 0V$          | R <sub>DESAT_on</sub> | -       | 900     | -       | Ω      |

### 1.5.5 Thermal Shutdown

| Donomotor                    | Conditions | Cymbol               |         | Units   |         |        |

|------------------------------|------------|----------------------|---------|---------|---------|--------|

| Parameter                    |            | Symbol               | Minimum | Typical | Maximum | Ullits |

| Thermal Shutdown Temperature | -          | T <sub>TSD_th</sub>  | -       | 160     | -       | °C     |

| Thermal Shutdown Hysteresis  | -          | T <sub>TSD_hys</sub> | -       | 20      | -       | °C     |

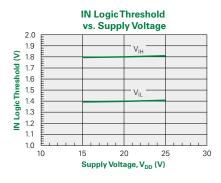

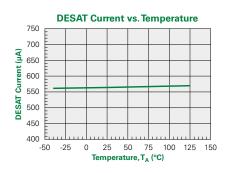

### 1.5.6 IN

| Parameter                  | Conditions          | Symbol             |         | Units   |         |        |

|----------------------------|---------------------|--------------------|---------|---------|---------|--------|

| raiailletei                | Conditions          | Syllibol           | Minimum | Typical | Maximum | Oilles |

| Input Voltage              |                     | ·                  |         |         |         |        |

| Level Logic High           |                     | V <sub>IH</sub>    | 2.2     | -       | -       |        |

| Logic Level Low            | -                   | V <sub>IL</sub>    | -       | -       | 1       | V      |

| Hysteresis                 |                     | V <sub>I_hys</sub> | 0.2     | 0.4     | -       |        |

| Input Current              |                     |                    |         |         |         |        |

| High Level                 | V <sub>IH</sub> =5V | I <sub>IH</sub>    | -       | 55      | 70      |        |

| Low Level                  | V <sub>IL</sub> =0V | I <sub>IL</sub>    | -       | -       | -       | μА     |

| Input Pull-Down Resistance | V <sub>IN</sub> =5V | R <sub>IN</sub>    | -       | 110     | -       | kΩ     |

### 1.5.7 FAULT

| Parameter                                  | Conditions                  | Conditions Symbol N    |         | Units   |         |        |

|--------------------------------------------|-----------------------------|------------------------|---------|---------|---------|--------|

| rarameter                                  | Conditions                  |                        | Minimum | Typical | Maximum | Ullits |

| Output Low Voltage                         | I <sub>FAULT_OL</sub> =20mA | V <sub>FAULT_OL</sub>  | -       | -       | 0.8     | V      |

| Output Leakage Current                     | V <sub>FAULT</sub> =20V     | I <sub>FAULT</sub>     | -       | 0.1     | 10      | μΑ     |

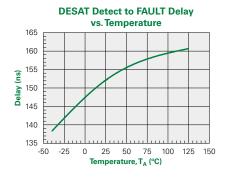

| DESAT Detect to FAULT<br>Propagation Delay | -                           | t <sub>FAULT_pZL</sub> | -       | 152     | -       | ns     |

| MUTE Pulse Width                           | DESAT Detect = TRUE         | t <sub>MUTE</sub>      | -       | 2       | -       | ms     |

### 1.5.8 Soft Shutdown

| Parameter                                    | Conditions                  | Symbol                   | Value   |         |         | Units  |

|----------------------------------------------|-----------------------------|--------------------------|---------|---------|---------|--------|

| raiailletei                                  |                             |                          | Minimum | Typical | Maximum | Oilles |

| Soft Shutdown Threshold Voltage              | INSOFT Falling              | V <sub>INSOFT_th</sub>   | 2.3     | 2.6     | 3       | V      |

| Soft Shutdown Hysteresis                     | -                           | V <sub>INSOFT_hys</sub>  | -       | 0.4     | -       | V      |

| OUTSOFT Peak Sink Current                    | -                           | loutsoft                 | -       | 900     | -       | mA     |

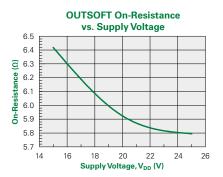

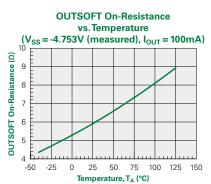

| OUTSOFT On-Resistance                        | I <sub>OUTSOFT</sub> =100mA | R <sub>OUTSOFT_on</sub>  | -       | 5.92    | 15      | Ω      |

| DESAT Detect to OUTSOFT<br>Propagation Delay | -                           | t <sub>OUTSOFT_pZL</sub> | -       | 125     | -       | ns     |

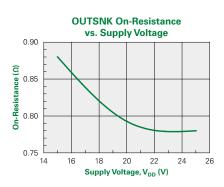

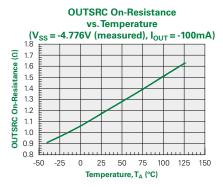

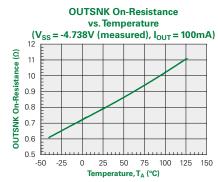

### 1.5.9 Gate Drive Output

| Parameter                       | Conditions                  | Symbol                 | Value                  |         |                       | Units |

|---------------------------------|-----------------------------|------------------------|------------------------|---------|-----------------------|-------|

| raiailletei                     |                             | Syllibol               | Minimum                | Typical | Maximum               | Units |

| High Level Output Voltage       | I <sub>OUTSRC</sub> =-100mA | V <sub>OUTSRC</sub>    | V <sub>DD2</sub> - 0.2 | -       | -                     | V     |

| Low Level Output Voltage        | I <sub>OUTSNK</sub> = 100mA | V <sub>OUTSNK</sub>    | -                      | -       | V <sub>SS</sub> +0.15 | V     |

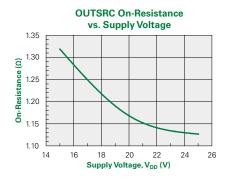

| OUTSRC On-Resistance            | I <sub>OUTSRC</sub> =-100mA | R <sub>OUTSRC_on</sub> | -                      | 1.17    | 2                     | Ω     |

| OUTSNK On-Resistance            | I <sub>OUTSNK</sub> =100mA  | R <sub>OUTSNK_on</sub> | -                      | 0.79    | 1.5                   | 22    |

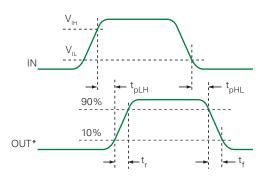

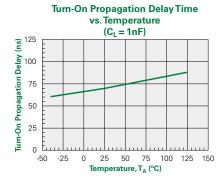

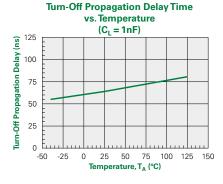

| Turn-On Propagation Delay Time  | C <sub>LOAD</sub> =1nF      | t <sub>pLH</sub>       | -                      | 70      | 125                   |       |

| Turn-Off Propagation Delay Time | C <sub>LOAD</sub> =1nF      | t <sub>pHL</sub>       | -                      | 65      | 125                   | ne    |

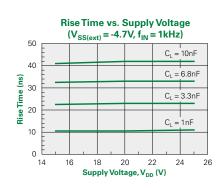

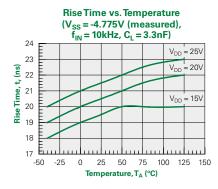

| Rise Time                       | C <sub>LOAD</sub> =1nF      | t <sub>r</sub>         | -                      | 10      | 20                    | ns    |

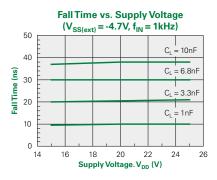

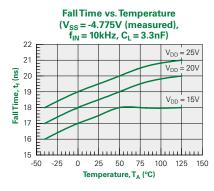

| Fall Time                       | C <sub>LOAD</sub> =1nF      | t <sub>f</sub>         | -                      | 10      | 20                    |       |

### 1.6 Thermal Characteristics

| Parameter                              | Symbol        | Rating | Units |

|----------------------------------------|---------------|--------|-------|

| Thermal Impedance, Junction to Ambient | $\theta_{JA}$ | 60     | °C/W  |

| Thermal Impedance, Junction to Case    | $\theta_{JC}$ | 28     | °C/W  |

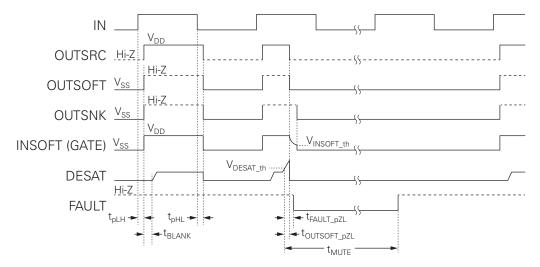

# 1.7 Timing Diagram

\*OUT is the node formed by connecting OUTSRC, OUTSNK and OUTSOFT together.

### 2 Performance Data

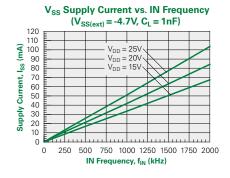

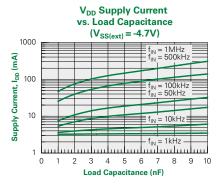

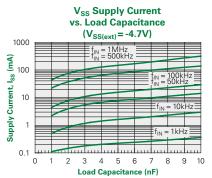

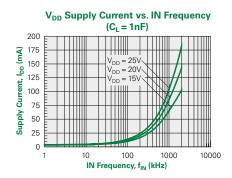

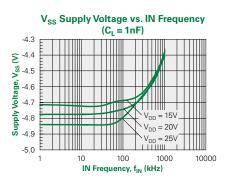

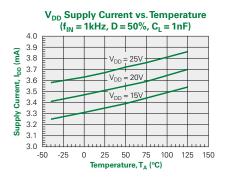

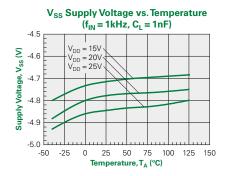

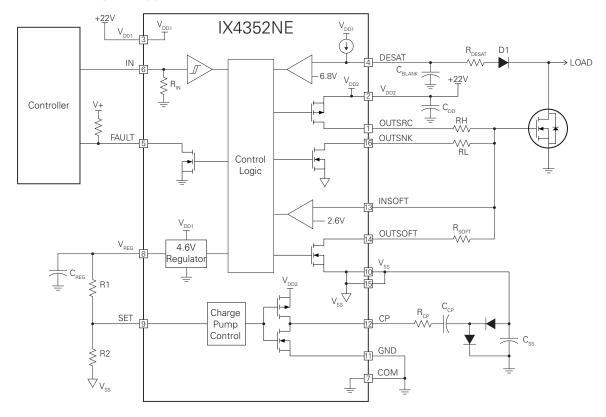

Unless otherwise noted,  $V_{DD}$ =20V,  $V_{IL}$ =0V,  $V_{IH}$ =5V, R1=40.2k $\Omega$ , R2=44.2k $\Omega$ , R2=33 $\Omega$ ,  $C_{CP}$ =68nF, $T_A$ =25°C, and values are typical. Component locations are as shown in Figure 1, "IX4352NE Typical Application Circuit" on page 11. " $V_{SS(ext)}$ " is the voltage applied to  $V_{SS}$  with the charge pump disabled and " $V_{SS}$  (measured)" is at  $T_A$ =25°C.

### 3 Functional Description

The IX4352NE is designed to provide the gate drive for high power SiC MOSFETs and IGBTs.

Figure 1. IX4352NE Typical Application Circuit

### 3.1 Power Supplies

The IX4352NE requires only a single positive supply (V<sub>DD</sub>) to provide SiC and IGBT gate driver functionality by generating the negative supply voltage (V<sub>SS</sub>) required to efficiently turn off SiC and IGBT power switches. V<sub>DD</sub> provides the supply voltage for both  $V_{DD1}$  at pin 3 and  $V_{DD2}$  at pin 2.  $V_{DD1}$  is the logic and control circuitry supply voltage while  $V_{\text{DD2}}$  is the positive supply for OUTSRC and the charge pump. In order to minimize coupling of the noise generated by transitions of OUTSRC and the charge pump to the logic and control circuits,  $V_{DD1}$  and  $V_{DD2}$  are not internally connected. Therefore it is important these two supply pins be tied together on the printed circuit board to ensure  $V_{DD1} = V_{DD2}$ . An on-board regulator provides the low voltage supply (V<sub>REG</sub>) used by the internal control logic while the on-board charge pump generates the pulses necessary to create V<sub>SS</sub>, the negative supply voltage.

#### 3.2 Logic Input (IN)

IN, the gate driver logic input, is a TTL and CMOS logic level compatible high-speed Schmitt trigger buffer that controls the gate driver outputs: OUTSRC,

OUTSNK, and OUTSOFT. The input voltage logic thresholds have a nominal 400mV of hysteresis and are referenced to COM. On startup, after  $V_{DD}$  and  $V_{SS}$  exceed their Under Voltage Lock Out thresholds and under non-fault operating conditions, IN controls the state of the gate driver outputs according to the table below:

Table 1: IN Gate Control Truth Table

| IN | OUTSRC     | OUTSNK     | OUTSOFT    |

|----|------------|------------|------------|

| 0  | Off (Hi-Z) | On (Low)   | On (Low)   |

| 1  | On (High)  | Off (Hi-Z) | Off (Hi-Z) |

### 3.3 Gate Drive Outputs

The IX4352NE has three gate drive outputs. Two power outputs, OUTSRC and OUTSNK, are each rated for a maximum peak current of 9A while the third output, OUTSOFT, is rated for a typical peak current of 900mA. Separate source and sink high current outputs allow independent adjustment of the discrete power SiC MOSFET or IGBT turn-on and turn-off transactions by means of a single resistor for each output. An internal non-adjustable dead time prevents cross conduction of the source and sink outputs.

#### **IX4352NE**

During normal operation whenever IN, the gate control input, is driven to a logic low the lower rated current sink output, OUTSOFT, turns on concurrently with OUTSNK. These operations can be seen in Figure 2, "Logic Diagram" on page 13. In the logic diagram these normal operation transactions can be seen in the first high-to-low transition of IN.

### 3.4 Internal 4.6V Regulator (V<sub>REG</sub>)

An internal 4.6V regulator provides power for the IX4352NE low voltage control circuitry and requires an external 4.7 $\mu$ F bypass capacitor (C<sub>REG</sub>). Capable of sourcing up to 10mA, V<sub>REG</sub> is utilized to set the negative supply voltage level and optionally to power the LED of an external optocoupler.

### 3.5 Negative Supply Voltage (V<sub>SS</sub>) Generation

The IX4352NE voltage inverting charge pump circuitry outputs  $V_{SS}$ , a regulated negative supply voltage. Operating in a closed-loop mode, the charge pump generates  $V_{SS}$  from  $V_{DD}$  with regulation being achieved by sensing the  $V_{SS}$  voltage with respect to  $V_{REG}$  at the SET input by means of the resistor divider R1 and R2. See Figure 1, "IX4352NE Typical Application Circuit" on page 11 for the circuit configuration. The charge pump inverter requires five external components: two discrete diodes, two ceramic capacitors, and a peak output current limiting resistor (R<sub>CP</sub>). For  $V_{DD}$ =20V,  $V_{SS}$  is set by the R1 and R2 resistor divider given in the following equation:

$$V_{SS} = -(V_{REG} - V_{SET}) \cdot \frac{R2}{R1} + V_{SET}$$

Setting  $V_{REG}$  = 4.66V (the typical open circuit voltage) and  $V_{SET}$  = 0.11V, the equation reduces to:

$$V_{SS} = -4.55 \cdot \left(\frac{R2}{R1}\right) + 0.11$$

Where R1+R2 ~ 100kOhm

To improve efficiency, low leakage Schottky diodes may be used in the charge pump voltage inverter circuitry.

The recommended value of the charge pump inverter components is:

- 1.  $R_{CP} = 33\Omega$

- 2.  $C_{CP} = 68nF$

- 3.  $C_{SS} = 10 \mu F$

To prevent damaging the charge pump output and minimize power dissipation, the value of  $R_{\text{CP}}$  must not be reduced.

To ensure a negative voltage gate bias under all operating conditions, the charge pump is always active whenever the V<sub>DD</sub> UVLO is cleared.

For applications where an external V<sub>SS</sub> supply is available and preferred, the following steps need to be taken:

- Connect the external negative supply to V<sub>SS</sub> at pins 10 and 15.

- Connect SET to COM to deactivate the charge pump.

- 3. Leave the charge pump output, CP, pin 12, open.

When using an external negative voltage supply, it is important not to exceed the  $V_{SS}$  voltage and current limitations.

#### 3.6 Desaturation Detection and Protection

DESAT detection occurs when the SiC or IGBT power transistor goes into an over-current condition causing the voltage across the transistor to exceed a predetermined threshold chosen by the designer. When the power switch is in an overcurrent situation, the desaturation protection circuit ensures the safety of the external SiC MOSFET or IGBT during turn-off.

The DESAT pin monitors the voltage across the power transistor via the input circuitry between the DESAT input and the SiC MOSFET drain or the IGBT collector. When the sum of the drain or collector voltage plus the voltage drop of the DESAT input circuitry exceeds the DESAT Threshold Voltage (V<sub>DESAT th</sub>), typically 6.8V, the FAULT output goes low, the internal MUTE function is activated and a controlled turn-off sequence is initiated. OUTSRC is turned off and OUTSOFT is turned on. The OUTSOFT 900mA sink capability provides an initial slow turn-off of the external SiC MOSFET or IGBT. When the GATE voltage decreases to the Soft Shutdown Threshold Voltage (V<sub>INSOFT\_th</sub>), typically 2.6V, OUTSNK turns on and quickly pulls the GATE to V<sub>SS</sub>. This two-step turn-off avoids dangerous dV/dt transient over-voltage spikes across the external SiC MOSFET or IGBT.

When a DESAT fault is detected, the MUTE feature is activated. MUTE holds the FAULT output low and masks logic transitions applied to IN for a nominal 2ms duration. Once the MUTE timer expires, FAULT is released and the input will begin normal operation with the next low to high transition of IN. During the DESAT fault event, transitioning IN from high to low anytime during MUTE will not affect the soft shutdown sequence or resumption of normal operation.

#### Figure 2. Logic Diagram

The DESAT detection and two-step turn-off sequence is illustrated in Figure 2, "Logic Diagram" on page 13. In the logic diagram, this sequence begins with the second rising edge of IN.

To avoid a false desaturation detect event when the external SiC MOSFET or IGBT is turned on, the IX4352 provides a nominal 250ns DESAT detect blanking time (t<sub>BLANK</sub>) beginning when OUTSRC transitions from OFF (Hi-Z) to ON (High) causing the gate drive output voltage to rise. While OUTSRC is off, the DESAT input is internally pulled low. To accomplish the fixed internal blanking time and to precondition the DESAT input for the fully turned on SiC MOSFET or IGBT, an internal pull down MOSFET at the DESAT input remains active for the duration of the blanking period.

For applications where the IX4352NE is not used to perform the DESAT fault detection voltage measurement, the DESAT input at pin 4 must be properly conditioned to prevent false detects and the subsequent shutdown procedure by the internal circuitry. The simplest solution is to use a low-value resistor from the DESAT input to COM that will ensure the voltage across the pull down resistor is sufficiently lower than the minimum detect threshold limit to provide noise immunity without the need for a noise suppression capacitor.

Although the nominal internal blanking duration is fixed at 250ns it can be extended by means of an external capacitor,  $C_{BLANK}$ , installed from the DESAT input to COM. Once the internal pull down is released, the additional blanking duration is set by the time it takes to charge the total external capacitive loading of the DESAT input up to  $V_{DESAT\_th}$ . The value of  $C_{BLANK}$  is the difference between the total

capacitance required to obtain the desired blanking period less the capacitive loading of the other components on DESAT.

### 3.7 DESAT Input Component Selection

The value of  $R_{\text{DESAT}}$  is determined by the peak surge current permitted through diode D1 and the maximum voltage across the external power transistor. When IN is high and the power SiC MOSFET is on, the voltage at the DESAT input is calculated by the following equation.

$$V_{DESAT} = \, I_{DESAT} \cdot R_{DESAT} + V_f + V_{DS}$$

Substitute  $V_{CE}$  for  $V_{DS}$  when using an IGBT.

where V<sub>f</sub> is the forward voltage drop of D1.

For a desired drain-to-source desaturation voltage detect threshold ( $V_{DS-th}$ ), the equation is:

$$V_{DESAT\_th} - V_{DS\_th} = I_{DESAT} \cdot R_{DESAT} + n_{Vf}$$

Substitute  $V_{CE\ th}$  for  $V_{DS\ th}$  when using an IGBT.

where "n" is the number of series diodes in the DESAT detection input circuit.

Using multiple series diodes improves DESAT detection consistency by minimizing  $R_{DESAT}$ . Larger values of  $R_{DESAT}$  lessens DESAT detection uniformity due to variations of  $I_{DESAT}$ . This of course assumes the diode is operating above its forward bias knee voltage with a forward current of  $I_{DESAT}$ .

### 3.8 DESAT Blanking Time Stretching

Extending the blanking period is easily accomplished by the addition of an external capacitor to the DESAT input. Blanking time extension is the difference between the nominal 250ns fixed internal blanking period and the required total blanking time of the design. The equation for the total blanking time is given in the following equation.

$$t_{TOTAL} = 250ns + \frac{V_{DESAT\_th} \cdot C_{TOTAL}}{I_{DESAT}}$$

Where  $C_{TOTAL}$  is the total external capacitance seen by the DESAT input pin. For the design example shown in Figure 1, "IX4352NE Typical Application Circuit" on page 11,  $C_{TOTAL}$  is the sum of  $C_{BLANK}$  and  $C_{J}$ , the junction capacitance of D1.  $C_{BLANK}$  is calculated as follows:

$$C_{BLANK} = \frac{(t_{TOTAL} - 250ns) \cdot I_{DESAT}}{V_{DESAT\ th}} - \frac{C_J}{n}$$

Where "n" is the number of series diodes in the DESAT detection input circuit.

Optionally the total capacitance may include the junction capacitance of a protection zener diode from DESAT to COM. Because this additional junction capacitance is added to  $C_{TOTAL}$  it reduces the calculated value of  $C_{BL\,ANK}$ .

Junction capacitance of reversed biased diodes is voltage dependent so it is important to consult the manufacturer's data sheets for the correct value.

#### 3.9 Thermal Shutdown

Thermal protection circuity pulls FAULT low, turns off OUTSRC, turns on both OUTSNK and OUTSOFT when the IX4352NE internal junction temperature reaches a nominal +160°C. The charge pump remains active during thermal shutdown to ensure the power IGBT outputs are off. After the internal junction temperature decreases by approximately 20°C, the device returns to normal operation.

#### 3.10 FAULT Output

The FAULT output indicates the IX4352NE has detected a fault condition. An open-drain NMOS at the FAULT output pulls low whenever one of the four monitored fault conditions is detected. They are:

- V<sub>DD</sub> Under Voltage Lock Out.

FAULT output goes low until V<sub>DD</sub> UVLO clears.

OUTSRC is turned off.

OUTSNK and OUTSOFT go low.

Charge pump is disabled.

- V<sub>SS</sub> Under Voltage Lock Out.

FAULT output goes low until V<sub>SS</sub> UVLO clears.

OUTSRC is turned off.

OUTSNK and OUTSOFT go low.

Charge pump is unaffected by fault, continues running.

- DESAT detection.

FAULT output goes low for a nominal 2ms.

OUTSRC is turned off.

OUTSOFT goes low.

Gate voltage crosses V<sub>INSOFT\_th</sub>

OUTSNK goes low.

Charge pump is unaffected by fault, continues running.

- Thermal Shut Down.

FAULT output goes low until TSD clears.

OUTSRC is turned off.

OUTSNK and OUTSOFT go low.

Charge pump is unaffected by fault, continues running

When the UVLO and TSD faults clear, the IX4352NE returns to normal operation and the gate driver outputs immediately transition to comply with the current IN logic state.

When the DESAT fault clears, the FAULT output remains low until the 2ms MUTE timer expires. The OUTSNK and OUTSOFT outputs remain low until the next low to high IN transition after the MUTE timer expires.

# 4 Manufacturing Information

### 4.1 Moisture Sensitivity

All plastic encapsulated semiconductor packages are susceptible to moisture ingression. Littelfuse classifies its plastic encapsulated devices for moisture sensitivity according to the latest version of the joint industry standard, **IPC/JEDEC J-STD-020**, in force at the time of product evaluation. We test all of our products to the maximum conditions set forth in the standard, and guarantee proper operation of our devices when handled according to the limitations and information in that standard as well as to any

limitations set forth in the information or standards referenced below.

Failure to adhere to the warnings or limitations as established by the listed specifications could result in reduced product performance, reduction of operable life, and/or reduction of overall reliability.

This product carries a Moisture Sensitivity Level (MSL) classification as shown below, and should be handled according to the requirements of the latest version of the joint industry standard **IPC/JEDEC J-STD-033**.

| Device   | Moisture Sensitivity Level (MSL) Classification |  |

|----------|-------------------------------------------------|--|

| IX4352NE | MSL 1                                           |  |

#### 4.2 ESD Sensitivity

This product is ESD Sensitive, and should be handled according to the industry standard JESD-625.

### 4.3 Soldering Profile

Provided in the table below is the **IPC/JEDEC J-STD-020** Classification Temperature (T<sub>C</sub>) and the maximum dwell time the body temperature of these surface mount devices may be (T<sub>C</sub> - 5)°C or greater. The Classification Temperature sets the Maximum Body Temperature allowed for these devices during reflow soldering processes.

| Device   | Classification Temperature (T <sub>C</sub> ) | Dwell Time<br>(t <sub>p</sub> ) | Max Reflow Cycles |

|----------|----------------------------------------------|---------------------------------|-------------------|

| IX4352NE | 260°C                                        | 30 seconds                      | 3                 |

#### 4.4 Board Wash

Littelfuse recommends the use of no-clean flux formulations. Board washing to reduce or remove flux residue following the solder reflow process is acceptable provided proper precautions are taken to prevent damage to the device. These precautions include but are not limited to: using a low pressure wash and providing a follow up bake cycle sufficient to remove any moisture trapped within the device due to the washing process. Due to the variability of the wash parameters used to clean the board, determination of the bake temperature and duration necessary to remove the moisture trapped within the package is the responsibility of the user (assembler). Cleaning or drying methods that employ ultrasonic energy may damage the device and should not be used. Additionally, the device must not be exposed to halide flux or solvents.

15

#### 4.5 Mechanical Dimensions

#### 4.5.1 IX4352NE 16-Pin Narrow SOIC

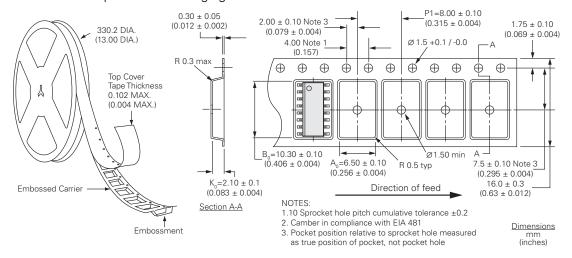

### 4.5.2 IX4352NETR Tape & Reel Packaging

**Disclaimer Notice** - Information furnished is believed to be accurate and reliable. However, users should independently evaluate the suitability of and test each product selected for their own applications. Littlefuse products are not designed for, and may not be used in, all applications. Read complete Disclaimer Notice at http://www.littlefuse.com/disclaimer-electronics