# **CPC2501M**Voltage Controlled, Normally Closed, 60 V, 1.84 A Solid State Relay

#### **Features**

- 1-Form-B (Normally closed) relay

- Internal control circuitry Self-actuating Fault protection timer

- 600 mΩ Maximum On-resistance at 25°C

- 60V peak AC or DC load voltage

- Load Current

1.84 A<sub>RMS</sub> Continuous

5 A Peak

- Fast Turn-on: 170 μs maximum

- Small 6×6 [mm] thermally enhanced QFN package

# **Applications**

- Door chime bypass

Derives power from standard 2-wire chime supply

System BOM savings and reduced PCB demands

- Building Automation

- Internet of Things (IoT)

- Security

- Voltage controlled relay

# **Description**

The CPC2501M incorporates a normally closed (1-Form-B) solid state relay switch with an integrated circuit specifically designed to control and manage the relay state based upon the applied voltage.

When configured for video doorbell applications, the CPC2501M becomes a self-actuating, non-isolated solid state relay that provides the ringing chime bypass function necessary to ensure proper video and chime operation. In addition to superior performance over video doorbells implemented with discrete devices, it offers superior power handling of 2.5W, a fast response time of 170 µs, fault protection circuitry, and the industry's highest load current of 1.84A. The CPC2501M provides reduced BOM costs and printed circuit board real estate demands through integration.

# **Ordering information**

| Part Number | Description                                               |

|-------------|-----------------------------------------------------------|

| CPC2501MTR  | QFN-16 with exposed pads in Tape and Reel (3000 pcs/reel) |

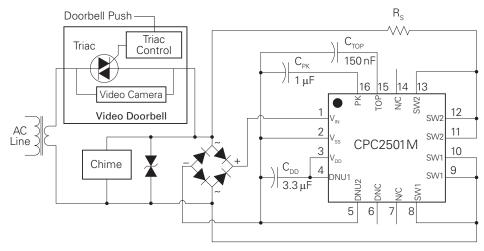

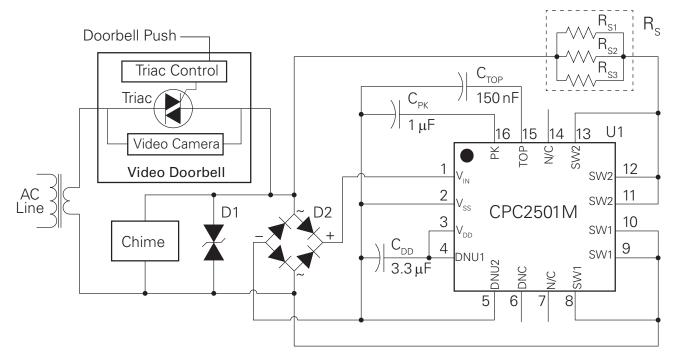

Figure 1. CPC2501M Typical Video Doorbell Application Circuit

| 1. | Speci | ifications                                             | 3    |

|----|-------|--------------------------------------------------------|------|

|    | 1.1   | Pinout                                                 | 3    |

|    | 1.2   | Pin Descriptions                                       | 3    |

|    | 1.3   | Absolute Maximum Ratings                               | 4    |

|    | 1.4   | Recommended Operating Conditions                       | 4    |

|    | 1.5   | Thermal Characteristics                                | 4    |

|    | 1.6   | Electrical Characteristics                             | 5    |

|    | 1.7   | Activation Delay Test Configuration and Timing Diagram | 5    |

| 2. | Perfo | rmance Data                                            | 6    |

| 3. | Funct | tional Description                                     | 7    |

|    | 3.1   | Description of Functional Blocks                       | 7    |

|    | 3.2   | Typical Video Doorbell Implementation                  | 8    |

|    | 3.3   | Resistive Load                                         | 9    |

|    | 3.4   | Voltage Regulator                                      | 9    |

|    | 3.5   | Solid State Switch                                     | 9    |

|    | 3.6   | Peak Detection                                         | 9    |

|    | 3.7   | Time-Out Protection                                    | . 10 |

|    | 3.8   | Power Considerations                                   | . 10 |

|    | 3.9   | Reference Design and BOM                               | . 11 |

| 4. | Manu  | ufacturing Information                                 | .12  |

|    | 4.1   | Moisture Sensitivity                                   | . 12 |

|    | 4.2   | ESD Sensitivity                                        | . 12 |

|    | 4.3   | Soldering Profile                                      | . 12 |

|    | 4.4   | Board Wash                                             | . 12 |

|    | 4.5   | Mechanical Dimensions                                  | . 13 |

# 1. Specifications

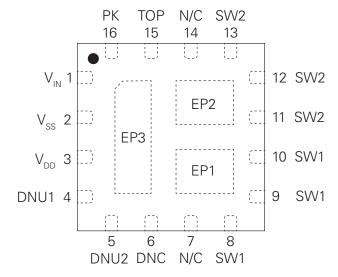

# 1.1 Pinout

# 1.2 Pin Descriptions

| Pin        | Name            | Туре    | Description                                                                                                 |  |

|------------|-----------------|---------|-------------------------------------------------------------------------------------------------------------|--|

| 1          | V <sub>IN</sub> | Power   | Supply voltage. Positive full wave rectified voltage from diode bridge                                      |  |

| 2          | $V_{SS}$        | Power   | Supply voltage return. Negative voltage from diode bridge                                                   |  |

| 3          | $V_{DD}$        | Output  | Regulated supply voltage for internal circuitry. Connect capacitor from $V_{DD}$ to $V_{SS}$ .              |  |

| 4          | DNU1            | _       | Do Not Use: Connect to V <sub>DD</sub>                                                                      |  |

| 5          | DNU2            | _       | Do Not Use: Connect to V <sub>SS</sub>                                                                      |  |

| 6          | DNC             | _       | Do Not Connect: Do not connect this pin.                                                                    |  |

| 7          | N/C             | _       | No Connection: Not internally connected.                                                                    |  |

| 8, 9, 10   | SW1             | I/O     | Switch terminal 1                                                                                           |  |

| 11, 12, 13 | SW2             | I/O     | Switch terminal 2                                                                                           |  |

| 14         | N/C             | _       | No Connection: Not internally connected.                                                                    |  |

| 15         | TOP             | Output  | Envelope tracking voltage of V <sub>IN</sub> . Connect capacitor from TOP to V <sub>SS</sub> . <sup>1</sup> |  |

| 16         | PK              | Output  | Peak voltage of V <sub>IN</sub> . Connect capacitor from PK to V <sub>SS</sub> . <sup>1</sup>               |  |

| EP1        | SW1             | Thermal | Thermal pad for SW1 power MOSFET. Connect to SW1, pins 8, 9 and 10. <sup>2</sup>                            |  |

| EP2        | SW2             | Thermal | Thermal pad for SW2 power MOSFET. Connect to SW2, pins 11, 12 and 13. <sup>2</sup>                          |  |

| EP3        | DNC             | Thermal | Thermal pad for the Control IC. Do not connect to this pad. <sup>2</sup>                                    |  |

<sup>&</sup>lt;sup>1</sup> See text regarding capacitor selection.

<sup>&</sup>lt;sup>2</sup> Package bottom side exposed pads EP1, EP2 and EP3 must be soldered to printed circuit board lands. See instructions in <u>Section 1.5 Thermal Characteristics on page 4.</u>

## 1.3 Absolute Maximum Ratings

Unless otherwise noted all voltages are with respect to  $V_{SS}$  and all electrical ratings are at  $T_{\Delta}$  = 25 °C.

| Parameter                                                  | Rating       | Unit |

|------------------------------------------------------------|--------------|------|

| V <sub>IN</sub> , V <sub>PK</sub> , V <sub>TOP</sub>       | -0.3 to +60  | V    |

| SW1 to SW2                                                 | -60 to +60   | V    |

| V <sub>DD</sub> , DNU1, DNU2                               | -0.3 to +5.5 | V    |

| Switch Peak Load Current (I <sub>L</sub> ) (for t < 16 ms) | 5            | А    |

| Total Power Dissipation <sup>1</sup>                       | 2.5          | W    |

| ESD Rating, Human Body Model                               | ±2           | kV   |

| Ambient Temperature (T <sub>A</sub> )                      | -40 to +85   | °C   |

| Virtual Junction Temperature $(T_{vj})$                    | +125         | °C   |

| Storage Temperature (T <sub>stg</sub> )                    | -40 to +150  | °C   |

Absolute Maximum Ratings are stress ratings. Stresses in excess of these ratings can cause permanent damage to the device. Functional operation of the device at conditions beyond those indicated in the operational sections of this data sheet is not implied.

## 1.4 Recommended Operating Conditions

| Davamatav                          | Symbol          | Va  | Units |                  |

|------------------------------------|-----------------|-----|-------|------------------|

| Parameter                          |                 | Min | Max   | Units            |

| V <sub>IN</sub> to V <sub>SS</sub> | V <sub>IN</sub> | _   | 44    | V                |

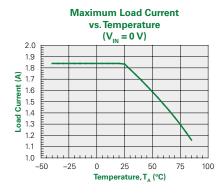

| Switch Load Current                | IL              | _   | 1.84  | A <sub>RMS</sub> |

#### 1.5 Thermal Characteristics

| Parameter                           | Symbol        | Rating | Units |

|-------------------------------------|---------------|--------|-------|

| Thermal Impedance, Junction to Air  | $\theta_{JA}$ | 40     | K/W   |

| Thermal Impedance, Junction to Case | $\theta_{JC}$ | 3      | K/W   |

**Note:** The thermal impedance values listed above and the total power dissipation rating stated in the Absolute Maximum Ratings table are based on measurements done on a 1.57 mm thick FR4 printed circuit board with the QFN bottom side exposed pads soldered to copper lands on the PCB. Each of the component side EP1 and EP2 PCB lands for SW1 and SW2 are thermally and electrically connected to a 70 µm thick (2 ounce) copper heat spreading shape of 0.75 square inches on the non-component side of the PCB by two 0.3 mm copper filled vias. It may be necessary to enlarge the SW1 and SW2 thermal lands shown in <u>Section 4.5.2 CPC2501M Recommended Land Pattern on page 13</u> to accommodate the thermal vias and to reduce the trace length connection to their pins.

It is not necessary to thermally connect EP3 to a heat spreading shape on the non-component side of the board.

$<sup>^{1}</sup>$  Derate linearly 25 mW/°C for  $T_{A}$  > 25 °C

#### 1.6 Electrical Characteristics

Unless otherwise noted, the Electrical Characteristics ratings are over the operational ambient temperature range of  $-40\,^{\circ}\text{C}$  to  $+85\,^{\circ}\text{C}$ .

Typical values are characteristic of the device at  $T_A$  = +25 °C, and are the result of engineering evaluations. They are provided for information purposes only, and are not part of the manufacturing test requirements.

| Dovomatav                                                             | Canditions                                                             | Comple of            | Value   |         |         |       |  |

|-----------------------------------------------------------------------|------------------------------------------------------------------------|----------------------|---------|---------|---------|-------|--|

| Parameter                                                             | Conditions                                                             | Symbol               | Minimum | Typical | Maximum | Units |  |

| Input Characteristics                                                 |                                                                        |                      |         |         |         |       |  |

| Input Current                                                         | $V_{IN} = 7V$ , $C_{DD} = 3.3 \mu\text{F}$                             |                      | 210     | 407     | 950     | μA    |  |

| input Current                                                         | $V_{IN} = 3.3 \text{ V}, C_{DD} = 3.3 \mu\text{F}$                     | V <sub>IN</sub>      | 130     | 245     | 545     | μΑ    |  |

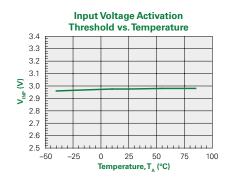

| Input Voltage Activation Threshold                                    | $C_{DD} = 3.3 \mu\text{F}$                                             | V <sub>INP</sub>     | 2.5     | 2.96    | 3.4     | V     |  |

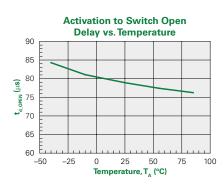

| Activation to Switch Open Delay                                       | Pulse $V_{IN}$ from 0V to 4.5V,<br>$V_{L} = 10V$ , $R_{L} = 1 k\Omega$ | t <sub>d_OPEN</sub>  | _       | 81      | 170     | μS    |  |

| Regulator                                                             |                                                                        |                      |         |         |         |       |  |

| Output Voltage                                                        | $V_{IN} = 7V$ , $C_{DD} = 3.3 \mu\text{F}$                             | \/                   | 4       | 4.6     | 5.2     | V     |  |

| Output voltage                                                        | $V_{IN} = 3.3 \text{ V}, C_{DD} = 3.3 \mu\text{F}$                     | - V <sub>DD</sub>    | 3.2     | 3.297   | 3.3     |       |  |

| Peak Detection To Deactivate                                          |                                                                        |                      |         |         |         |       |  |

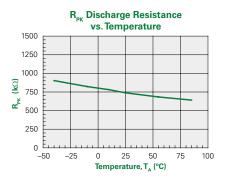

| PK Discharge Resistance                                               | _                                                                      | R <sub>PK</sub>      | 415     | 800     | 1325    | kΩ    |  |

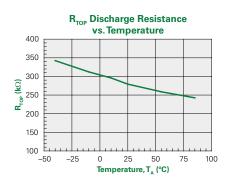

| TOP Discharge Resistance                                              | _                                                                      | R <sub>TOP</sub>     | 155     | 300     | 500     | KS2   |  |

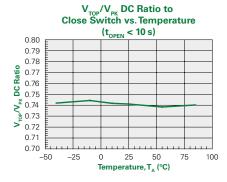

| V <sub>TOP_PK</sub> DC Ratio to Close Switch (Deactivation Threshold) | $C_{DD} = 3.3 \mu\text{F}$                                             | $V_{TOP} V_{PK}$     | 0.7     | 0.75    | 0.79    | _     |  |

| Time-Out Protection                                                   |                                                                        |                      |         |         |         |       |  |

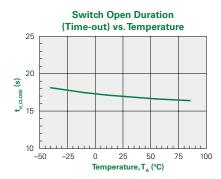

| Switch Open Duration (Time-out)                                       | $V_{IN} = 7V, C_{DD} = 3.3 \mu\text{F}$                                | t <sub>d_CLOSE</sub> | 10      | 17      | 25      | S     |  |

| Switch Characteristics                                                |                                                                        |                      |         |         |         |       |  |

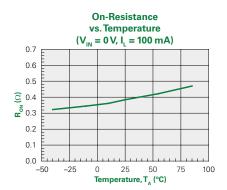

| On-Resistance (Switch Closed)                                         | $V_{IN} = 0V$ , $I_L = 100 \text{ mA}$ , $C_{DD} = 3.3 \mu\text{F}$    | R <sub>ON</sub>      | _       | 0.388   | 0.75    | Ω     |  |

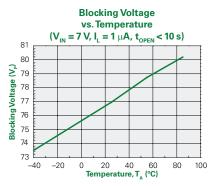

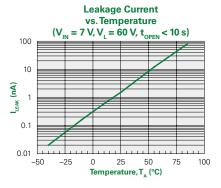

| Leakage Current (Switch Open)                                         | $V_{IN} = 7 \text{ V}, V_{L} = 60 \text{ V}, C_{DD} = 3.3 \mu\text{F}$ | I <sub>LEAK</sub>    | _       | _       | 1       | μА    |  |

## 1.7 Activation Delay Test Configuration and Timing Diagram

**Test Configuration**

**Timing Diagram**

# 2. Performance Data

Unless otherwise noted, the data presented in these graphs is typical and  $T_A = 25 \,^{\circ}\text{C}$

# 3. Functional Description

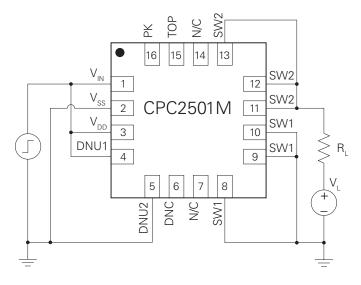

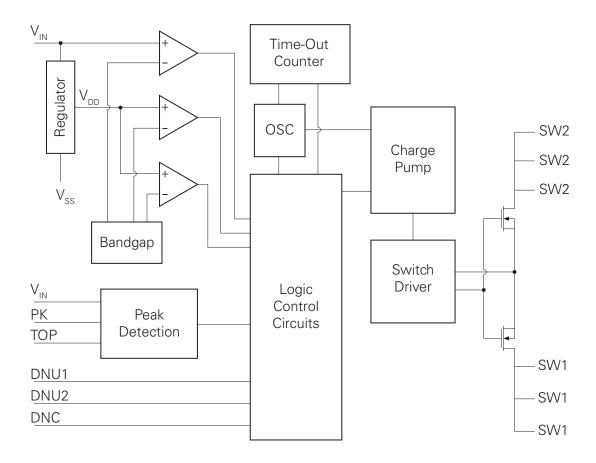

Figure 2. CPC2501M Functional Block Diagram

# 3.1 Description of Functional Blocks

**Regulator:** The regulator takes the full-wave rectified output of the diode bridge and outputs  $V_{\rm DD}$ , a regulated DC voltage used to power the internal functional blocks.

**Comparators:** Inputs to the comparators are the Bandgap reference voltages:  $V_{DD}$  and  $V_{IN}$ . The comparators monitor these voltages to ensure the CPC2501M switch activates at the correct voltage levels.

**Bandgap:** Provides a voltage reference to the internal circuits.

**Peak Detection:** This block is used to detect the presence, or absence of a valid doorbell push event.

**Oscillator:** The oscillator is enabled whenever a doorbell push is detected and validated by the Comparators and Logic Control Circuits. The oscillator AC output is used by the Charge Pump and Time-Out Counter.

**Charge Pump:** The charge pump is enabled upon detection of a doorbell push event. It converts the oscillator AC voltage into a DC voltage for the switch driver.

**Switch Driver:** This block uses the charge pump DC output to drive the Depletion-Mode MOSFET solid state switches.

**Output Switch:** Two 60V Depletion-Mode MOSFETs are set up in a common source series formation to block AC or DC voltages when open and to pass AC, or DC current when closed.

**Time-Out Counter:** When the CPC2501M normally closed switch is opened to allow the chime to operate. A timer is initiated to limit the active chime duration to a nominal 17 seconds. Following the time-out, circuitry in the Logic Control Circuits block will return the switch to its normally closed state thereby disabling the chime.

## 3.2 Typical Video Doorbell Implementation

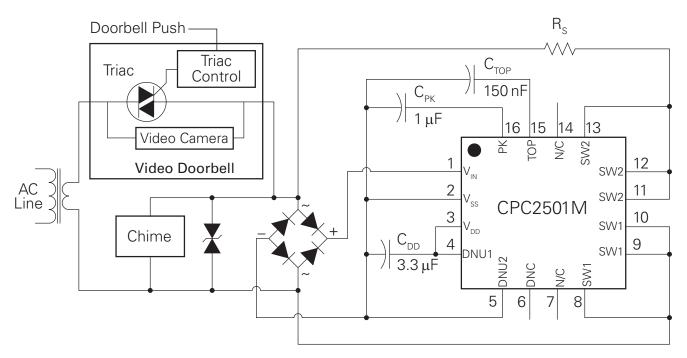

Figure 3. CPC2501M Typical Video Doorbell Application Circuit

A typical CPC2501M video doorbell application consists of four major elements: the power feed circuit, the chime, the video doorbell, and the CPC2501M chime bypass circuit. In the application circuit shown in Figure 3, the video doorbell, the chime, and the CPC2501M get their operating power from a power feed circuit consisting of a doorbell transformer and the two-wire cabling.

This design does not require any modifications to the ubiquitous two-wire feed circuit found in most homes and is compatible with a wide range of transformer voltages.

The chime bypass circuit consists of the CPC2501M, a rectifier diode bridge, three capacitors and a power resistor in series with the CPC2501M solid state switch. The CPC2501M derives its operating power from the voltage developed across  $\rm R_{\rm S}$  and  $\rm R_{\rm ON}$  (the resistance of the solid state switch) whenever the triac is activated.

In the idle state, the CPC2501M provides a low impedance shunt path across the chime thus enabling the video doorbell unit to draw operational power from the transformer. Whenever the doorbell is pushed, the Video Doorbell unit activates its triac, causing the current through the  $\rm R_S$  and  $\rm R_{ON}$  resistive load located in the chime bypass circuit, to increase substantially. The AC voltage developed across the resistive load by the increased current, is full wave rectified by the diode bridge and applied to the  $\rm V_{IN}$  and  $\rm V_{SS}$  power input pins. The positive output of the diode bridge is connected to  $\rm V_{IN}$  while the diode bridge negative output is connected to  $\rm V_{SS}$ .

When  $\rm R_S$  is sized properly, the resulting AC voltage generated by the increased current will activate CPC2501M. Activation occurs when the voltage applied to  $\rm V_{IN}$  exceeds  $\rm V_{INP}$ ; the Input Voltage Activation Threshold. When activated, the internal normally closed (Form-B) switch opens, which removes the low impedance chime bypass, making it possible for the chime to operate.

When the doorbell is released, the triac is deactivated causing the input voltage applied to  $V_{\rm IN}$  to decrease. Reduction of the input voltage applied to CPC2501M causes the voltages  $V_{\rm TOP}$  and  $V_{\rm PK}$  at pins TOP and PK to decay at a rate determined by their internal discharge resistors ( $R_{\rm TOP}$  and  $R_{\rm PK}$ ) and their external capacitors ( $C_{\rm TOP}$  and  $C_{\rm PK}$ ). When the ratio of  $V_{\rm TOP}$  to  $V_{\rm PK}$  reaches an internally set threshold the switch is return to its normally closed state, thereby reestablishing the low impedance shunt across the chime. Power to the video doorbell is now restored and the chime is deactivated, as it now lacks sufficient power to operate.

#### 3.3 Resistive Load

Control circuitry within the CPC2501M opens and closes the switch by detecting the video doorbell press and release. A doorbell push is detected and qualified by the magnitude of the voltage applied to  $V_{\rm IN}$ . Because the applied voltage is sourced from the voltage developed across the  $R_{\rm S}$  and  $R_{\rm ON}$  resistive load when the doorbell triac is activated, the input voltage  $(V_{\rm IN})$  to open the switch is a function of the current through the resistive load.

Selection of  $R_{\rm S}$  is based on a current level that represents the available current when the doorbell is pushed. Based on this current, the nominal value of  $R_{\rm S}$  where the CPC2501M will activate and open the switch can be determined by the following equation:

$$R_S = \frac{2V_f + V_{INP}}{I} - R_{ON}$$

Where:

- 2 V<sub>f</sub>=Voltage drop of the diode bridge.

- V<sub>INP</sub>=Typical V<sub>IN</sub> Threshold from Electrical Specifications table.

- R<sub>ON</sub>=Typical Switch On-Resistance from Electrical Specification table.

- I = Desired activation current.

### 3.4 Voltage Regulator

As shown in Figure 3, the input voltage is sourced from the positive output of the external diode bridge. The regulator takes the full wave rectified input voltage applied to  $V_{\text{IN}}$ , reduces it to level compatible with the internal low voltage circuitry and outputs it at the  $V_{\text{DD}}$  pin. Filtering of the reduced voltage is accomplished by  $C_{\text{DD}}$ , a  $3.3\,\mu\text{F}$  external capacitor. This filtered regulated voltage ( $V_{\text{DD}}$ ) provides the power required by the internal circuitry.

#### 3.5 Solid State Switch

In the idle state the normally closed solid state switch integrated into the CPC2501M is conducting, providing a low resistance shunt to bypass the chime. Consequently a very low input voltage is presented to the CPC2501M. Once the doorbell is pushed and  $\rm V_{IN}$  exceeds the threshold voltage, the switch opens and stops conducting. Now all the current flows through the chime allowing sufficient power for the chime to operate.

#### 3.6 Peak Detection

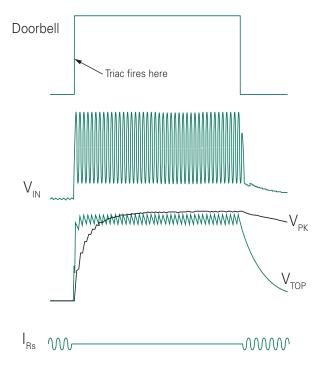

When the video doorbell is released, CPC2501M uses a peak detection method to determine when to close the solid state switch and restore the low impedance chime bypass shunt, allowing the video doorbell to regain operating power. Referring to Figure 3, capacitor C<sub>PK</sub> stores a voltage that corresponds to the peak excursion of the rectified AC waveform, while  $C_{TOP}$  stores a voltage that corresponds to the envelope of the rectified AC waveform. When the video doorbell button transitions from pressed to released, (triac stops conducting) the incoming rectified AC waveform exhibits a collapse in amplitude. Capacitor  $C_{PK}$  is needed to hold the peak excursion as long as possible while C<sub>TOP</sub> allows a "gentle" decay to track the waveform collapse. The CPC2501M monitors the voltage ratio of  $V_{TOP}$  to  $V_{PK}$  and closes the switch once V<sub>TOP</sub> decreases to approximately 75 % of V<sub>PK</sub> (Deactivation Threshold). This makes the CPC2501M compatible with digital chimes with up to  $850 \Omega$ impedance under typical conditions. Figure 4 shows the typical response waveforms of  $V_{PK}$  and  $V_{TOP}$  during doorbell press and release.

Figure 4. V<sub>PK</sub> and V<sub>TOP</sub> Response Waveforms

Charge and discharge times of  $V_{PK}$  and  $V_{TOP}$  are determined by on-chip charge and discharge resistors and their external capacitors  $C_{PK}$  and  $C_{TOP}$ . Note that the selection of  $C_{TOP}$  and  $C_{PK}$  will manifest itself as response delay from the triac, turning off to the actual closing of the switch. The following table shows the recommended values of the external capacitors and the estimated response delay. The solid state switch will close and begin conducting in less than three cycles after the video doorbell release, using the recommended  $C_{PK}$  and  $C_{TOP}$  values.

|                  | Internal Charging Resistor (k $\Omega$ ) | Internal Discharging<br>Resistor<br>(kΩ) | External<br>Capacitor<br>(μF) | Charging RC<br>Time Constant<br>(ms) | Discharging RC<br>Time Constant<br>(ms) | Switch Closure<br>Delay<br>(Cycles)* |

|------------------|------------------------------------------|------------------------------------------|-------------------------------|--------------------------------------|-----------------------------------------|--------------------------------------|

| $V_{PK}$         | 12.5                                     | 800                                      | 1                             | 12.5                                 | 800                                     | _                                    |

| V <sub>TOP</sub> | 12.5                                     | 300                                      | 0.15                          | 1.875                                | 45                                      | 2.7 (2.25)                           |

<sup>\*</sup>Delay cycles are calculated based on 60 Hz (50 Hz) AC signals.

#### 3.7 Time-Out Protection

Once activated the CPC2501M will open its normally closed switch and enable the Time-Out Counter. The Time-Out Counter will cause the switch to transition from open to closed if the CPC2501M determines the chime has been continuously enabled for approximately 17 s. If the amplitude of  $\rm V_{IN}$  does not decrease sufficiently for  $\rm V_{TOP}$  to decay below approximately 0.75  $\rm V_{PK}$  within 17 s, the switch will re-open for another 17 s time-out. The CPC2501M will continue to open and close the switch every 17 s until  $\rm V_{IN}$  decreases and the ratio of  $\rm V_{TOP}$  to  $\rm V_{PK}$  ( $\rm V_{TOP}/\rm V_{PK}$ ) falls below the deactivation threshold.

#### 3.8 Power Considerations

Note that maximum power dissipation of the resistive load,  $R_S$  and  $R_{ON}$ , will occur while the triac is conducting and the CPC2501M switch is closed such as when a Time-Out event has occurred. Attention to proper power management must be taken into account during component selection and printed circuit board layout with respect to end product environmental operating conditions.

# 3.9 Reference Design and BOM

Figure 5. Reference Design

| Component                                           | Description                        | Manufacturer: Part Number                 | Qty. |

|-----------------------------------------------------|------------------------------------|-------------------------------------------|------|

| R <sub>S1</sub> , R <sub>S2</sub> , R <sub>S3</sub> | 10Ω, 5%, 2W                        | Generic Thick Film Chip Resistor          | 3    |

| C <sub>TOP</sub>                                    | 150 nF, 5 %, 100V, X7R             | General Purpose Ceramic Capacitor         | 1    |

| C <sub>PK</sub>                                     | 1 μF, 5 %, 100V, X7R               | General Purpose Ceramic Capacitor         | 1    |

| C <sub>DD</sub>                                     | 33 μF, 10 %, 16V, X7R              | General Purpose Ceramic Capacitor         | 1    |

| D1                                                  | Transient Voltage Suppressor Diode | Littelfuse: SMBJ33CA                      | 1    |

| D2                                                  | 60V, 2A Bridge Rectifier           | Taiwan Semiconductor: SBS26 or equivalent | 1    |

| U1                                                  | Chime Bypass IC                    | Littelfuse: CPC2501M                      | 1    |

The reference design shown above is set to activate with an approximate peak current of 1A.

# 4. Manufacturing Information

# 4.1 Moisture Sensitivity

All plastic encapsulated semiconductor packages are susceptible to moisture ingression. Littelfuse classifies its plastic encapsulated devices for moisture sensitivity according to the latest version of the joint industry standard,

**IPC/JEDEC J-STD-020**, in force at the time of product evaluation. We test all of our products to the maximum conditions set forth in the standard, and guarantee proper operation of our devices when handled according to the limitations and information in that standard, as well as to any limitations set forth in the information, or standards referenced below.

Failure to adhere to the warnings or limitations as established by the listed specifications could result in reduced product performance, reduction of operable life, and/or reduction of overall reliability.

This product carries a Moisture Sensitivity Level (MSL) classification as shown below, and should be handled according to the requirements of the latest version of the joint industry standard **IPC/JEDEC J-STD-033**.

| Device   | Moisture Sensitivity Level (MSL) Classification |  |

|----------|-------------------------------------------------|--|

| CPC2501M | MSL1                                            |  |

# 4.2 ESD Sensitivity

This product is ESD Sensitive, and should be handled according to the industry standard JESD-625.

# 4.3 Soldering Profile

Provided in the table below is the **IPC/JEDEC J-STD-020** Classification Temperature ( $T_c$ ) and the maximum dwell time ( $T_c - 5$  °C). The Classification Temperature sets the Maximum Body Temperature allowed for these devices during reflow soldering processes.

| Device   | Classification Temperature (T <sub>C</sub> ) | Dwell Time (t <sub>p</sub> ) | Max Reflow Cycles |

|----------|----------------------------------------------|------------------------------|-------------------|

| CPC2501M | 260°C                                        | 30 seconds                   | 3                 |

#### 4.4 Board Wash

Littelfuse recommends the use of no-clean flux formulations. Board washing to reduce, or remove flux residue following the solder reflow process is acceptable, provided proper precautions are taken to prevent damage to the device. These precautions include, but are not limited to: Using a low pressure wash and providing a follow-up bake cycle sufficient to remove any moisture trapped within the device, due to the washing process. Due to the variability of the wash parameters used to clean the board, determination of the bake temperature and duration necessary to remove the moisture trapped within the package is the responsibility of the user (assembler). Cleaning, or drying methods that employ ultrasonic energy may damage the device and should not be used. Additionally, the device must not be exposed to halide flux or solvents.

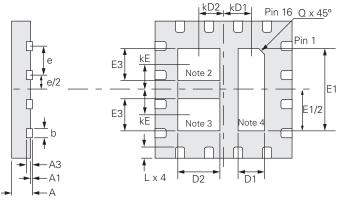

#### 4.5 Mechanical Dimensions

# 4.5.1 CPC2501M 16-Pin QFN Package

| SYMBOL   | М        | ILLIMET  | ER   |  |

|----------|----------|----------|------|--|

| OTIVIDOL | MIN.     | TYP.     | MAX. |  |

| А        | 0.80     | 0.85     | 0.90 |  |

| A1       | 0.00     | 0.02     | 0.05 |  |

| А3       | (        | 0.20 REF |      |  |

| b        | 0.35     | 0.40     | 0.45 |  |

| D        | 6        | 6.00 BSC | )    |  |

| D1       | 1.10     | 1.15     | 1.20 |  |

| D2       | 1.80     | 1.85     | 1.90 |  |

| Е        | 6        | 6.00 BSC | ,    |  |

| E1       | 3        | 3.60 BSC | )    |  |

| E3       | 1.35     | 1.40     | 1.45 |  |

| е        | ,        | 1.27 BSC | ,    |  |

| kD1      | ,        | 1.22 BSC | ,    |  |

| kD2      | 1.08 BSC |          |      |  |

| kE       | 1.10 BSC |          |      |  |

| L        | 0.45     | 0.50     | 0.55 |  |

| Q        | 0.30     | 0.35     | 0.40 |  |

| SYMBOL   | INCHES     |       |       |

|----------|------------|-------|-------|

| STIVIDOL | MIN.       | TYP.  | MAX.  |

| А        | 0.031      | 0.033 | 0.035 |

| A1       | 0.000      | 0.001 | 0.002 |

| A3       | 0.008 REF. |       |       |

| b        | 0.014      | 0.016 | 0.018 |

| D        | 0.236 BSC  |       |       |

| D1       | 0.043      | 0.045 | 0.047 |

| D2       | 0.071      | 0.073 | 0.075 |

| E        | 0.236 BSC  |       |       |

| E1       | 0.142 BSC  |       |       |

| E3       | 0.053      | 0.055 | 0.057 |

| е        | 0.050 BSC  |       |       |

| kD1      | 0.048 BSC  |       |       |

| kD2      | 0.043 BSC  |       |       |

| kE       | 0.043 BSC  |       |       |

| L        | 0.018      | 0.020 | 0.022 |

| Q        | 0.012      | 0.014 | 0.016 |

## NOTES:

- 1. Controlling dimension: millimeters.

- 2. Exposed pad: EP2, connect to SW2 pins.

3. Exposed pad: EP1, connect to SW1 pins.

4. Exposed pad: EP3, no connection.

- 5. All exposed pads must be soldered to their PCB lands.

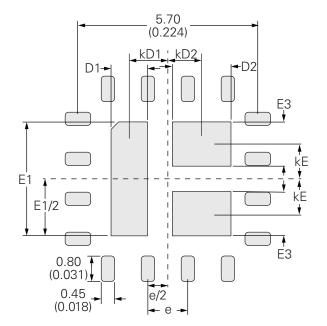

## 4.5.2 CPC2501M Recommended Land Pattern

| SYMBOL | mm   | inch  |

|--------|------|-------|

| D1     | 1.15 | 0.045 |

| D2     | 1.85 | 0.073 |

| E1     | 3.60 | 0.142 |

| E3     | 1.40 | 0.055 |

| е      | 1.27 | 0.050 |

| kD1    | 1.22 | 0.048 |

| kD2    | 1.08 | 0.043 |

| kE     | 1.10 | 0.043 |

|        |      |       |

NOTE: It may be necessary to enlarge the EP1 and EP2 thermal lands shown above to accommodate the thermal vias and to reduce the trace length connection

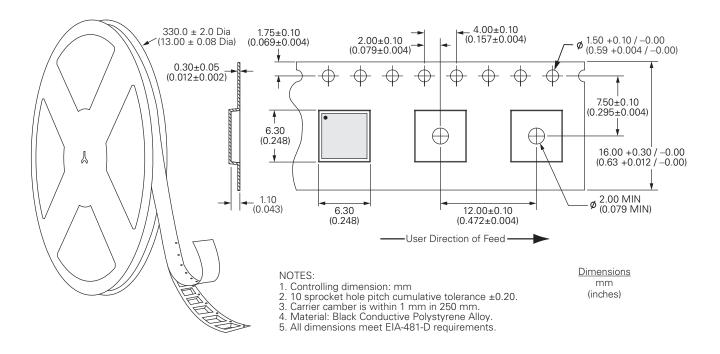

## 4.5.3 Tape and Reel Dimensions

**Disclaimer Notice** - Information furnished is believed to be accurate and reliable. However, users should independently evaluate the suitability of and test each product selected for their own applications. Littelfuse products are not designed for, and may not be used in, all applications. Read complete Disclaimer Notice at <a href="https://www.littelfuse.com/disclaimer-electronics">https://www.littelfuse.com/disclaimer-electronics</a>