### **Web Resources**

Download ECAD models, order samples, and find technical recources at www.littelfuse.com

#### Size Table

| Metric | EIA  |

|--------|------|

| 3216   | 1206 |

### **Absolute Maximum Ratings**

| Continuous                                            | MLN Series  | Units |

|-------------------------------------------------------|-------------|-------|

| Steady State Applied Voltage:                         |             |       |

| DC Voltage Range (V <sub>M(DC)</sub> )                | 5.5 - 18    | V     |

| Operating Ambient Temperature Range (T <sub>A</sub> ) | -40 to +125 | °C    |

| Storage Temperature Range (T <sub>STG</sub> )         | -40 to +150 | °C    |

For ratings of individual members of a series, see device ratings and specifications table

# **Description**

The MLN SurgeArray<sup>TM</sup> Suppressor is designed to help protect components from transient voltages that exist at the circuit board level. This device provides four independent suppressors in a single leadless chip in order to reduce part count and placement time as well as save space on printed circuit boards.

SurgeArray™ Suppressor are intended to suppress ESD, EFT and other transients in order to protect integrated circuits or other sensitive components operating at any voltage up to 18VDC. SurgeArray™ Suppressor are rated to the IEC 61000-4-2 human body model ESD to help products attain EMC compliance. The array offers excellent isolation and low crosstalk between sections.

The inherent capacitance of the SurgeArray<sup>™</sup> Suppressor permits it to function as a filter/suppressor, thereby replacing separate Zener/capacitor combinations.

The MLN array is manufactured using the Littelfuse Multilayer technology process and is similar to the Littelfuse ML and MLE Series of discrete leadless chips.

### **Features & Benefits**

- RoHS Compliant

- Four individual devices in one chip

- ESD rated to IEC 61000-4-2 (Level 4)

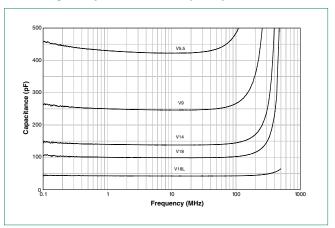

- AC characterized for impedance and capacitance

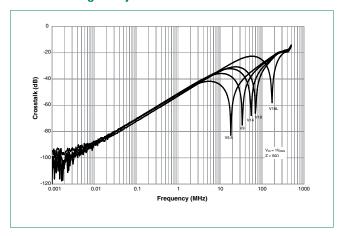

- Low adjacent channel crosstalk, -55dB at 10MHz (Typ)

- Low leakage

- Operating voltage up to 18VM(DC)

- -40°C to 125°C operating temp range

- Low-profile, PCMCIA compatible

# **Applications**

- Data, Diagnostic I/O Ports

- Analog Signal/Sensor Lines

- Portable/Hand-Held Products

- Mobile Communications/ Cellular Phones

- Computer/DSP Products

- Industrial Instruments Including Medical

### **Device Ratings and Specifications Any Single Section**

| Maximum Ratings (125°C) |                                             | Specifications (25°C)                                |                                                          |                                                                                      |       |                                      |     |         |                                     |      |            |

|-------------------------|---------------------------------------------|------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|-------|--------------------------------------|-----|---------|-------------------------------------|------|------------|

| Part Number             | Maximum<br>Continuous<br>Working<br>Voltage | Maximum Non-<br>repetitive Surge<br>Current (8/20µs) | Maximum<br>Non-repetitive<br>Surge Energy<br>(10/1000µs) | petitive Clamping Voltage (at Energy Noted 8/20us)  Voltage (Note1)  Voltage (Note1) |       | Typical ESD Supression               |     | DC Test | Capacitance<br>at 1 MHz<br>(1V p-p) |      |            |

|                         | V <sub>M(DC)</sub>                          | I <sub>TM</sub>                                      | TM C                                                     | V <sub>c</sub>                                                                       |       | (Note 2) (Note<br>8kV Contact 15kV A |     | VN(DC)  | VN(DC)                              | •    | te 4)<br>C |

|                         | M(DC)                                       | I IVI                                                |                                                          | Peak                                                                                 | Clamp | Peak                                 | Min | Max     | TYP                                 | MAX  |            |

|                         | (V)                                         | (A)                                                  | (J)                                                      | (V)                                                                                  | (V)   | (V)                                  | (V) | (V)     | (V)                                 | (pF) | (pF)       |

| V5.5MLN41206            | 5.5                                         | 30                                                   | 0.10                                                     | 15.5 at 2A                                                                           | 60    | 35                                   | 45  | 7.10    | 10.8                                | 430  | 520        |

| V9MLN41206              | 9.0                                         | 30                                                   | 0.10                                                     | 23.0 at 2A                                                                           | 95    | 50                                   | 75  | 11.0    | 16.0                                | 250  | 300        |

| V14MLN41206             | 14.0                                        | 30                                                   | 0.10                                                     | 30.0 at 2A                                                                           | 110   | 55                                   | 85  | 15.9    | 20.3                                | 140  | 175        |

| V18MLN41206             | 18.0                                        | 30                                                   | 0.10                                                     | 40.0 at 2A                                                                           | 165   | 63                                   | 100 | 22.0    | 28.0                                | 100  | 125        |

| V18MLN41206L            | 18.0                                        | 30                                                   | 0.05                                                     | 50.0 at 1A                                                                           | 200   | 95                                   | 130 | 25.0    | 35.0                                | 45   | 75         |

#### Notes:

- 1. Tested to IEC61000-4-2 Human Body Model (HBM) discharge test circuit.

- Direct discharge to device terminals (IEC preffered test method).

Corona discharge through air (represents actual ESD event)

- 4. Capacitance may be customized, contact Sales.

- 5. The typical capacitance rating is the discrete component test result.

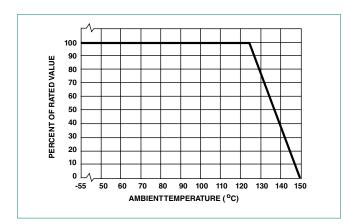

Fig. 1 Peak Current and Energy Derating Curve

For applications exceeding 125°C ambient temperature, the peak surge current and energy ratings must be

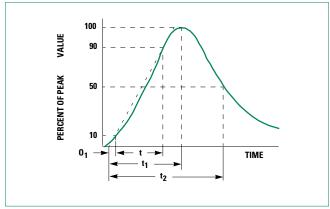

Fig. 2 Peak Pulse Current Test Waveform for Clamping **Voltage**

0, = Virtual Origin of Wave = Time from 10% to 90% of Peak  $T_1 = Rise Time = 1.25 x T$

T. = Decay Time

(Impulse Duration)

#### Example:

For an 8/20 µs Current Waveform:  $8\mu s = T_s = Rise Time$  $20\mu s = T_2 = Virtual Time to Half Value$

# **Typical Performance Curves**

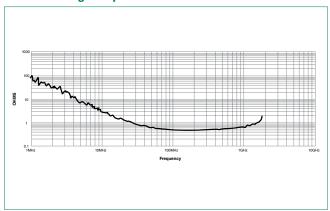

Fig. 3 Equivalent Series Resistance

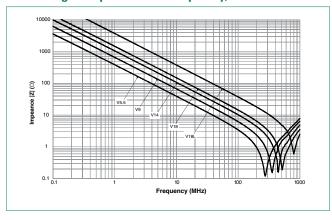

### Fig. 4 Impedance vs Frequency, 1206 Size

# **Typical Performance Curves (continued)**

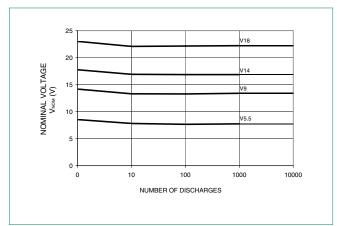

Fig. 5 Nominal Voltage Stability to IEC 1000-4-2 (8kV Contact Method, One Section)

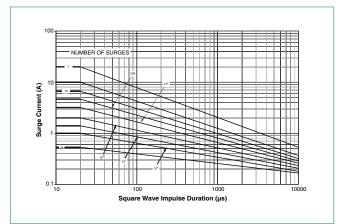

Fig. 6 1206 Size Pulse Rating for Long Duration Surges (Any Single Section)

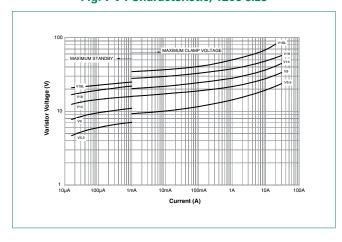

Fig. 7 V-I Characteristic, 1206 size

Fig. 8 Capacitance vs Frequency, 1206 Size

Fig. 9 Adjacent Channel Crosstalk

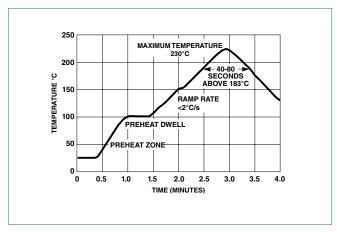

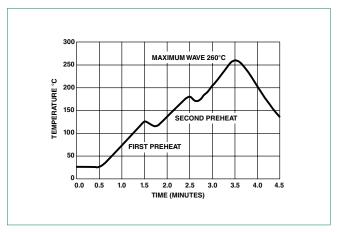

### Lead (Pb) Soldering Recommendations

The principal techniques used for the soldering of components in surface mount technology are IR Re-flow and Wave soldering. Typical profiles are shown on the right.

The recommended solder for the MLN suppressor is a 62/36/2 (Sn/Pb/Ag), 60/40 (Sn/Pb) or 63/37 (Sn/Pb). Littelfuse also recommends an RMA solder flux.

Wave soldering is the most strenuous of the processes. To avoid the possibility of generating stresses due to thermal shock, a preheat stage in the soldering process is recommended, and the peak temperature of the solder process should be rigidly controlled.

When using a reflow process, care should be taken to ensure that the MLN chip is not subjected to a thermal gradient steeper than 4 degrees per second; the ideal gradient being 2 degrees per second. During the soldering process, preheating to within 100 degrees of the solder's peak temperature is essential to minimize thermal shock.

Once the soldering process has been completed, it is still necessary to ensure that any further thermal shocks are avoided. One possible cause of thermal shock is hot printed circuit boards being removed from the solder process and subjected to cleaning solvents at room temperature. The boards must be allowed to cool gradually to less than 50°C before cleaning.

Fig. 10 Reflow Solder Profile

Fig. 11 Wave Solder Profile

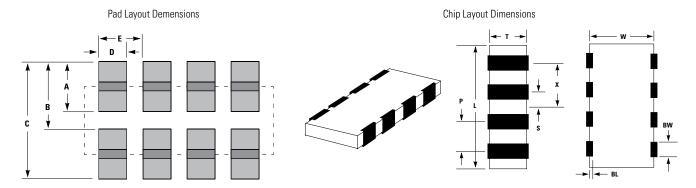

### **Product Dimensions (mm)**

| Di        | 1206 Size           |                    |  |  |  |  |

|-----------|---------------------|--------------------|--|--|--|--|

| Dimension | IN                  | MM                 |  |  |  |  |

| Α         | 0.035               | 0.890              |  |  |  |  |

| В         | 0.065               | 1.650              |  |  |  |  |

| С         | 0.100               | 2.540              |  |  |  |  |

| D         | 0.018               | 0.460              |  |  |  |  |

| E         | 0.030               | 0.790              |  |  |  |  |

| L         | 0.126 -/+0.008      | 3.200 -/+0.200     |  |  |  |  |

| W         | 0.063 -/+0.008      | 1.600 -/+0.200     |  |  |  |  |

| Т         | 0.053 Max           | 1.350 Max          |  |  |  |  |

| BW        | 0.016 -/+0.004      | 0.410 -/+0.100     |  |  |  |  |

| BL        | 0.007 +0.01/- 0.002 | 0.180 +0.25/-0.050 |  |  |  |  |

| P         | 0.030 Ref           | 0.760 Ref          |  |  |  |  |

| Χ         | 0.045 -/+0.004      | 1.140 -/+0.100     |  |  |  |  |

| S         | 0.015 -/+0.004      | 0.380 -/+0.100     |  |  |  |  |

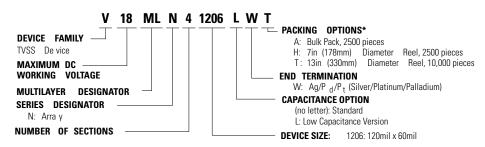

### **Part Numbering System**

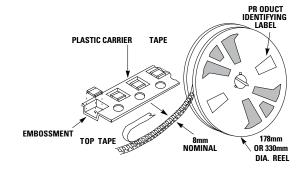

# Packaging\*

|             | Quantity                      |                              |                           |  |

|-------------|-------------------------------|------------------------------|---------------------------|--|

| Device Size | 13" Inch Reel<br>("T" Option) | 7" Inch Reel<br>("H" Option) | Bulk Pack<br>("A" Option) |  |

| 1206        | 10,000                        | 2,500                        | 2,500                     |  |

<sup>\*(</sup>Packaging) It is recommended that parts be kept in the sealed bag provided and that parts be used as soon as possible when removed from bags.

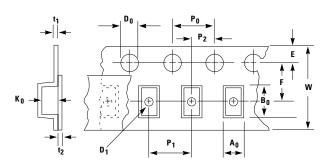

### **Tape and Reel Specifications**

| Symbol         | Description                                                  | Dimensions in Millimeters                    |

|----------------|--------------------------------------------------------------|----------------------------------------------|

| A <sub>o</sub> | Width of Cavity                                              | Dependent on Chip Size to Minimize Rotation. |

| B <sub>o</sub> | Length of Cavity                                             | Dependent on Chip Size to Minimize Rotation. |

| K <sub>o</sub> | Depth of Cavity                                              | Dependent on Chip Size to Minimize Rotation. |

| W              | Width of Tape                                                | 8 -/+0.2                                     |

| F              | Distance Between Drive Hole Centers and Cavity Centers       | 3.5 -/+0.5                                   |

| E              | Distance Between Drive Hole Centers and Tape Edge            | 1.75 -/+0.1                                  |

| P <sub>1</sub> | Distance Between Cavity Center                               | 4 -/+0.1                                     |

| P <sub>2</sub> | Axial Distance Between Drive Hole Centers and Cavity Centers | 2 -/+0.1                                     |

| $P_{o}$        | Axial Distance Between Drive Hole Centers                    | 4 -/+0.1                                     |

| D <sub>o</sub> | Drive Hole Diameter                                          | 1.55 -/+0.05                                 |

| D <sub>1</sub> | Diameter of Cavity Piercing                                  | 1.05 -/+0.05                                 |

| T <sub>1</sub> | Embossed Tape Thickness                                      | 0.3 Max                                      |

| T <sub>2</sub> | Top Tape Thickness                                           | 0.1 Max                                      |

#### Notes:

Conforms to EIA-481-1, Revision A

<sup>•</sup> Can be supplied to IEC publication 286-3