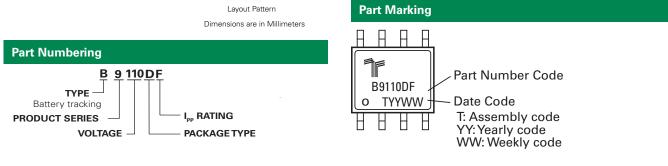

# B9110DF, Single Port, ± polarity tracking SLIC protector

RoHS CN PO

### **Agency Approvals**

| Agency    | Agency File Number |

|-----------|--------------------|

| <b>91</b> | E133083            |

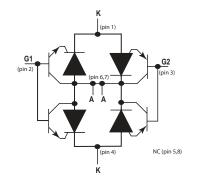

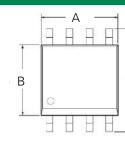

Pinout

| К  | 1 <sub>0</sub> | 8 |   | NC |

|----|----------------|---|---|----|

| G1 | 2              | 7 |   | А  |

| G2 | 3              | 6 |   | А  |

| К  | 4              | 5 |   | NC |

|    |                |   | J |    |

| Pin # | Pin Name | Description                               |

|-------|----------|-------------------------------------------|

| 1, 4  | К        | Connect to subscriber lines (Tip or Ring) |

| 2     | G1       | Connect to battery (-V <sub>BAT</sub> )   |

| 3     | G2       | Connect to battery (+V <sub>BAT</sub> )   |

| 6, 7  | А        | Connect to ground (earth)                 |

| 5, 8  | NC       | Not connected                             |

## Schematic Symbol

### Description

This single port polarity programmable B9110DF protector is specifically designed to protect smart ringing SLICs with dual power supplies. This B9110DF will protect the SLIC interface against lightning induced surges and power fault events. It contains fast switching crowbarring structures that are compatible with the Basic levels outlined in ITU K.20, K.21. For compliance with the Enhanced levels, an additional resistor in series with tip and ring may be required. This programmable protector may also be beneficial for YD/T 950, TIA-968-B, GR-1089-Core Issue 6 and UL/EN/IEC 60950-1 compliance.

The SLIC chipset voltage reference may change as the on-hook/off-hook line condition changes. Therefore, this protector is referenced to the  $+V_{BAT}$  and  $-V_{BAT}$  references so that its protection thresholds follow these reference voltage changes by approximately 1.4V. The B9110DF gates utilize transistor gain networks so that a low 5 mA current level will activate these four separate protection structures. This allows for easier turn on during slow rising ac power fault events.

### Features

- High performance protection for SLICs with +  $V_{BAT}$  and - $V_{BAT}$  references and with changing  $V_{BAT}$  references

- Wide -110V to +110V programming range

- Low gate current triggering

- ESD Immunity(HBM): JESD22 Class 3B, ≥8KV

- MSL: Level 1 unlimited

- tracking crowbarring component

- Fails short circuit when surged in excess of its ratings to protect SLIC chipset

- Surge capability does not degrade after multiple surge events within its ratings

- RoHS compliant and lead-free

# Applications

- Wireless In the Local Loop (WLL)

- Voice applications which require regenerated POTS

- VoIP applications

- PBX

- FXS applications

- Digital Pair Gain systems (DPG) and Digital Loop Carrier systems (DLC)

- Small Office Home Office (SOHO)

# Absolute Maximum Ratings (T<sub>A</sub> =25°C)

| Symbol                  | Parameter                                                        | Test Conditions                                                    |              | Value   | Unit  |

|-------------------------|------------------------------------------------------------------|--------------------------------------------------------------------|--------------|---------|-------|

| V                       | Repetitive peak off-state voltage                                | $V_{G1(Line)} = 0, V_{G2} \ge +5 V$                                |              | -120    | - V   |

| V <sub>drm</sub>        |                                                                  | $V_{G2(Line)} = 0, V_{O}$                                          | +120         |         |       |

|                         |                                                                  | 2/10 µs (Telcordia G                                               | R-1089-CORE) | ±100    |       |

| I <sub>PPSM</sub>       | Non-repetitive peak impulse current<br>(see Notes 1, 2, 3 and 4) | 5/310 μs (K.20, K.21 open-circuit voltage<br>wave shape 10/700 μs) |              | ±45     | A     |

| 11.0141                 |                                                                  | 10/1000 µs (Telcordia GR-1089-CORE)                                |              | ±30     | _     |

|                         |                                                                  | 8/20 µs (IEC 61000-4-5, 2 <sup>nd</sup> Edition)                   |              | ±110    |       |

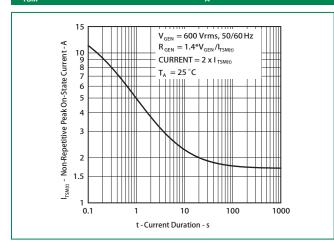

|                         |                                                                  |                                                                    | 0.2s         | 9.0     |       |

| I <sub>TSM</sub>        | Non repetitive peak on-state current                             | 50Hz / 60Hz (see Notes<br>1, 2, 3, 5 and 6)                        | 1s           | 5.0     | A     |

|                         |                                                                  |                                                                    | 900s         | 1.7     |       |

| $V_{\rm G1M}$           | Maximum negative battery supply voltage                          |                                                                    |              | -110    | V     |

| V <sub>G2M</sub>        | Maximum positive battery supply voltage                          |                                                                    |              | +110    | V     |

| $\Delta V_{\rm (BAT)M}$ | Maximum differential battery supply voltage                      |                                                                    |              | 220     | V     |

| T <sub>stg</sub>        | Storage temperature range                                        |                                                                    |              | -65-150 | °C    |

| TJ                      | Junction temperature                                             |                                                                    |              | -40-150 | °C    |

| TL                      | Maximum lead temperature for soldering during 10s                |                                                                    |              | 260     | °C    |

| R <sub>eja</sub>        | Junction to ambient thermal resistance                           |                                                                    |              | 55      | °C /W |

NOTES:

1. Initially the component must be in thermal equilibrium with T<sub>J</sub> = 25 °C. The surge may be repeated after the component returns to its initial conditions.

2. The rated current values may be applied to either of the Line to Ground terminal pairs. Additionally, both terminal pairs may have their rated current values applied simultaneously (in this case the Ground terminal current will be twice the rated current value of a single terminal pair).

3. Rated currents only apply if pins 6 & 7 (Ground) are connected together.

4. Applies for the following bias conditions:  $V_{G1}$  = -20 V to -110 V,  $V_{G2}$  = 0 V to +110 V.

5. EIA/JESD51-2 environment and EIA/JESD51-7 high effective thermal conductivity test board (multi-layer) connected with 0.6 mm printed wiring track widths.

6. Please refer to "I<sub>TSM</sub> Rating vs Current Duration" table on page 3.

### **Electrical Characteristics**

| Symbol                    | Parameter                           | Test Conditions                                                       | Max                                      | Unit       |    |

|---------------------------|-------------------------------------|-----------------------------------------------------------------------|------------------------------------------|------------|----|

|                           |                                     | $V_{\rm D} = V_{\rm DRM}, V_{\rm G1(Line)} = 0, V_{\rm G2} \ge +5  V$ | T <sub>A</sub> =25°C                     | -5         |    |

| .                         | Off-state current                   | (see Note 1)                                                          | T <sub>A</sub> =85°C                     | -50        |    |

| D                         |                                     | $V_{\rm D} = V_{\rm DRM}, V_{\rm G2(Line)} = 0, V_{\rm G1} \ge -5V$   | T <sub>A</sub> =25°C                     | +5         | μA |

|                           |                                     | (see Note 1)                                                          | T <sub>A</sub> =85°C                     | +50        |    |

| I <sub>G1(Line)</sub>     | Negative-gate Leakage current       | $V_{G1(Line)} = V_{G1M}$                                              | V <sub>G1(Line)</sub> = V <sub>G1M</sub> |            | μA |

| I <sub>G2(Line)</sub>     | Positive-gate Leakage current       | $V_{G2(Line)} = V_{G1M}$                                              |                                          | +5         | μA |

| V <sub>G1L(BO)</sub> Gate | Gate-Line impulse breakover voltage | y' = 100y' = 1000 (200  Note  2)                                      | 2/10µs                                   | -15        | V  |

|                           | Gate-Line impulse breakover voltage | V <sub>G1</sub> =-100V, I <sub>T</sub> =-100A (see Note 2)            | 10/100µs                                 | -11        |    |

| V                         | Gate-Line impulse breakover voltage | 1/2 = 100 1/2 = 1000 (coo Note 2)                                     | 2/10µs                                   | +15        | V  |

| V <sub>G2L(BO)</sub>      | Gate-Line impulse breakover voltage | V <sub>G2</sub> =+100V, I <sub>T</sub> =+100A (see Note 2)            | 10/100µs                                 | +11        |    |

| I <sub>H</sub>            | Holding current                     | V <sub>g1</sub> =-60V, I <sub>T</sub> =-1A, di/dt=1A/ms               |                                          | -150 (min) | mA |

| I <sub>G1T</sub>          | Negative-gate trigger current       | I <sub>T</sub> =-5A, t <sub>p(g)</sub> ≥20μs, V <sub>G1</sub> =-60V   |                                          | +5         | mA |

| I <sub>G2T</sub>          | Positive-gate trigger current       | l <sub>T</sub> =+5A, t <sub>p(g)</sub> ≥20μs, V <sub>G2</sub> =-      | -5                                       | mA         |    |

| V <sub>gt</sub>           | Gate trigger voltage                | I <sub>T</sub> =-3A, t <sub>p(g)</sub> ≥20μs, V <sub>GG</sub> =-1     | 1.4                                      | V          |    |

| C <sub>o</sub>            | Line-ground off-state capacitance   | f=1MHz,V <sub>p</sub> =-3V, G1 & G2 op                                | 110                                      | pF         |    |

NOTES:

1.  $\rm V_{\rm D}$  is the supply voltage during test

2. Voltage measurements should be made with an oscilloscope with limited bandwidth (20 MHz) to avoid high frequency noise.

# SIDACtor<sup>®</sup> Protection Thyristors

Programmable tracking Protection

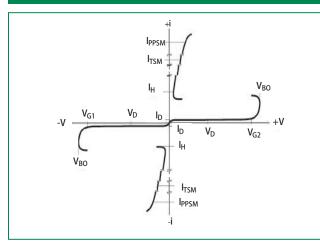

# V-I Characteristics

| Parameter                            | Symbol                            |

|--------------------------------------|-----------------------------------|

| Off-state current                    | I <sub>D</sub>                    |

| Repetitive peak off-state voltage    | V <sub>D</sub>                    |

| Holding current                      | I <sub>H</sub>                    |

| Non-repetitive peak impulse current  | I <sub>PPSM</sub>                 |

| Non repetitive peak on-state current | I <sub>TSM</sub>                  |

| Breakover voltage                    | V <sub>BO</sub>                   |

| Gate-Line impulse breakover voltage  | V <sub>G1</sub> , V <sub>G2</sub> |

# $I_{\text{TSM}}$ Rating vs Current Duration( $T_{A}$ =25°C)

# **SIDACtor**<sup>®</sup> **Protection Thyristors** Programmable tracking Protection

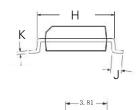

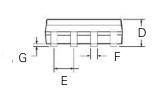

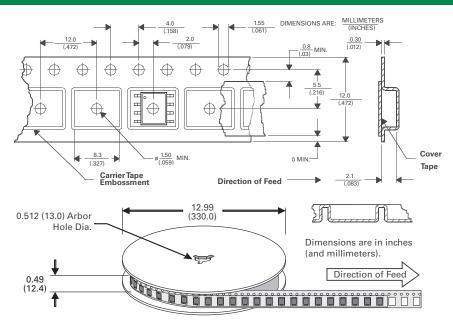

# Dimensions — MS-012 (Wide Body)

С

| Dimension | Inches |                    | Millimeters |      |  |

|-----------|--------|--------------------|-------------|------|--|

| DIMENSION | MIN    | MAX                | MIN         | MAX  |  |

| А         | 0.205  | 0.217              | 5.20        | 5.50 |  |

| В         | 0.205  | 0.217              | 5.20        | 5.50 |  |

| С         | 0.287  | 0.315              | 7.30        | 8.00 |  |

| D         | 0.067  | 0.083              | 1.70        | 2.10 |  |

| E         | 0.050  | 0.050 BSC 1.27 BSC |             | BSC  |  |

| F         | 0.014  | 0.020              | 0.36        | 0.51 |  |

| G         | 0.002  | 0.010              | 0.05        | 0.25 |  |

| Н         | 0.244  | 0.260              | 6.20        | 6.60 |  |

| J         | 0.022  | 0.043              | 0.55        | 1.10 |  |

| K         | 0.007  | 0.009              | 0.18        | 0.22 |  |

\* BSC = Basic Spacing between Centers

| Product Selector |              |             |                                          |          |                   |  |  |

|------------------|--------------|-------------|------------------------------------------|----------|-------------------|--|--|

| Part Number      | Part Marking | PackageType | Description                              | Quantity | Industry Standard |  |  |

| B9110DF          | B9110DF      | D           | MS-012 SMT 8-pin SOIC Tape and Reel Pack | 2000     | EIA-481-D         |  |  |

|                  |              |             |                                          |          |                   |  |  |

### Tape and Reel Specifications – MS-012 (Wide Body)

© 2017 Littelfuse, Inc. Specifications are subject to change without notice. Revised: 02/24/17

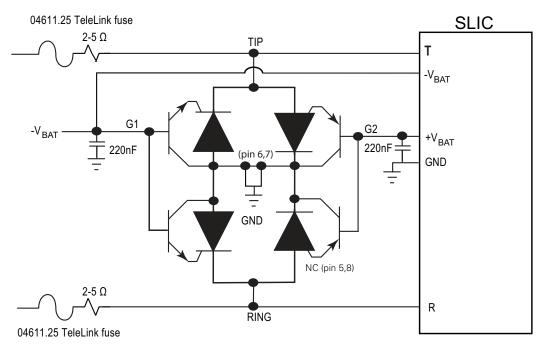

### **Operating and schematic explanation**

The MS-012 SMT (SOIC-8) Dual Polarity Battrax<sup>®</sup> is specifically designed to provide surge protection for SLIC (Subscriber Line Interface Circuit) cards implementing positive and negative ringing, which are used in many telecommunication applications. This single 8-pin component provides protection for both line conductors (TIP & RING) by shunting positive and negative surges to the ground reference.

The surges are diverted to ground through the SCRs which are connected between the TIP/RING conductors and the ground reference. These SCRs have a transistor buffered gate that provides a low current magnitude trigger level; typically 5 mA or less. The SCRs will reset when the magnitude of the loop current drops below the component's holding current parameter I<sub>µ</sub>.

This component's turn-on threshold tracks with both the positive and negative reference voltages of the SMART SLIC component. As the line conditions change from on-hook to off-hook, the SLIC reference voltage levels will also change in an effort to conserve energy. This tracking protection component will typically operate at +1.4V above + $V_{BAT}$  and at -1.4V below - $V_{BAT}$  during either surge conditions or power fault events. The buffered gate reduces the gate current needed to activate this component to approximately 5 mA.

The gate capacitors, which act as a charge reservoir, supply the needed current to trigger this component to the on-state and should be physically located in close proximity to the B9110DF gate leads. During slow rising ac power fault events, the discharge current of the capacitor ( $I_c = C dv/dt$ ) easily achieves the 5 mA threshold to activate the SCR. This solution below will comply with the power fault and surge requirements of GR-1089 Intra-building Port Type and the Basic level of ITU K20/21. For GR-1089 Port Type 3 and Enhanced level of ITU K20/21, the series resistor value may need to be increased. The TeleLink fuse complies with both GR-1089 intra-building and inter-building requirements and both Basic and Enhanced levels of the ITU Recommendations.