| V <sub>(BR)DSX</sub> / V <sub>(BR)DGX</sub> | R <sub>DS(on)</sub><br>(max) | I <sub>DSS</sub> (min) | Package |

|---------------------------------------------|------------------------------|------------------------|---------|

| 350V <sub>P</sub>                           | 22Ω                          | 130mA                  | SOT-89  |

#### **Features**

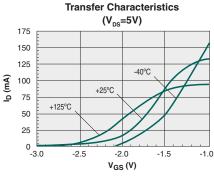

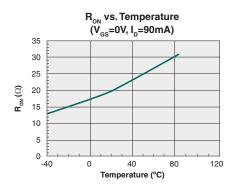

- $\bullet$  Offers Low  $\mathsf{R}_{\mathsf{DS}(\mathsf{on})}$  at Cold Temperatures

- R<sub>DS(on)</sub> 22Ω max. at 25°C

- High Input Impedance

- High Breakdown Voltage: 350V<sub>P</sub>

- Low  $V_{GS(off)}$  Voltage: -1.6 to -3.9V

- Small Package Size SOT-89

- Flammability Rating UL 94 V-0

## **Applications**

- Ignition Modules

- · Normally-On Switches

- Solid State Relays

- Converters

- · Telecommunications

- Power Supply

# Description

The CPC3720 is an N-channel, depletion mode, field effect transistor (FET) that utilizes IXYS Integrated Circuits Division's proprietary third-generation vertical DMOS process. The third-generation process realizes world class, high voltage MOSFET performance in an economical silicon gate process. Our vertical DMOS process yields a robust device, with high input impedance, for use in high power applications. The CPC3720 is a highly reliable FET device that has been used extensively in our solid state relays for industrial and telecommunications applications.

This device excels in power applications requiring low drain-source resistance, particularly in cold environments such as automotive ignition modules. The CPC3720 offers a low,  $22\Omega$  maximum, on-state resistance at  $25^{\circ}$ C.

The CPC3720 has a minimum breakdown voltage of  $350V_{\rm P}$ , and is available in an SOT-89 package. As with all MOS devices, the FET structure prevents thermal runaway and thermal-induced secondary breakdown.

## **Ordering Information**

| Part #     | Description                                                            |

|------------|------------------------------------------------------------------------|

| CPC3720CTR | N-Channel Depletion Mode FET, SOT-89 Pkg.<br>Tape and Reel (1000/Reel) |

## Package Pinout

(SOT-89)

## **Circuit Symbol**

# Absolute Maximum Ratings @ 25°C

| Parameter                 | Ratings          | Units   |  |

|---------------------------|------------------|---------|--|

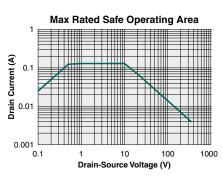

| Drain-to-Source Voltage   | 350              | $V_P$   |  |

| Gate-to-Source Voltage    | ±15              | $V_{P}$ |  |

| Pulsed Drain Current      | 600              | mA      |  |

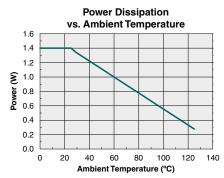

| Total Package Dissipation | 1.4 <sup>1</sup> | W       |  |

| Junction Temperature      | 150              | °C      |  |

| Operational Temperature   | -55 to +125      | °C      |  |

| Storage Temperature       | -55 to +125      | °C      |  |

<sup>1</sup> Mounted on FR4 board 1"x1"x0.062"

Absolute Maximum Ratings are stress ratings. Stresses in excess of these ratings can cause permanent damage to the device. Functional operation of the device at conditions beyond those indicated in the operational sections of this data sheet is not implied.

Typical values are characteristic of the device at +25°C, and are the result of engineering evaluations. They are provided for information purposes only, and are not part of the manufacturing testing requirements.

# **Electrical Characteristics @ 25°C (Unless Otherwise Noted)**

| Parameter                                        | Symbol                    | Conditions                                                          | Min  | Тур | Max  | Units          |

|--------------------------------------------------|---------------------------|---------------------------------------------------------------------|------|-----|------|----------------|

| Drain-to-Source Breakdown Voltage                | V <sub>(BR)DSX</sub>      | V <sub>GS</sub> = -5V, I <sub>D</sub> =100μA                        | 350  | -   | -    | V <sub>P</sub> |

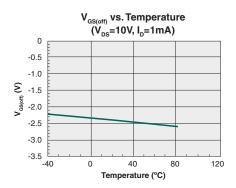

| Gate-to-Source Off Voltage                       | $V_{GS(off)}$             | $V_{DS} = 5V, I_{D} = 1mA$                                          | -1.6 | -   | -3.9 | V              |

| Change in V <sub>GS(off)</sub> with Temperatures | dV <sub>GS(off)</sub> /dT | $V_{DS} = 5V$ , $I_D = 1\mu A$                                      | -    | -   | 4.5  | mV/°C          |

| Gate Body Leakage Current                        | I <sub>GSS</sub>          | $V_{GS}$ =±15V, $V_{DS}$ =0V                                        | -    | -   | 100  | nA             |

| Drain-to-Source Leakage Current                  | I <sub>D(off)</sub>       | V <sub>GS</sub> = -5V, V <sub>DS</sub> =350V                        | -    | -   | 1    | μΑ             |

| Diam-to-Source Leakage Guitem                    |                           | V <sub>GS</sub> = -5V, V <sub>DS</sub> =280V, T <sub>A</sub> =125°C | -    | -   | 1    | mA             |

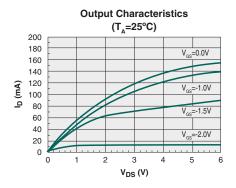

| Saturated Drain-to-Source Current                | I <sub>DSS</sub>          | V <sub>GS</sub> = 0V, V <sub>DS</sub> =15V                          | 130  | -   | -    | mA             |

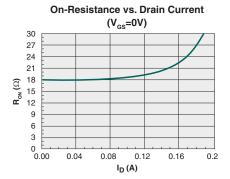

| Static Drain-to-Source ON-State Resistance       | R <sub>DS(on)</sub>       | V <sub>GS</sub> = 0V, I <sub>D</sub> =130mA                         | -    | -   | 22   | Ω              |

| Change in R <sub>DS(on)</sub> with Temperatures  | dR <sub>DS(on)</sub> /dT  | V <sub>GS</sub> = 0V, I <sub>D</sub> =130mA                         | -    | -   | 1.1  | %/°C           |

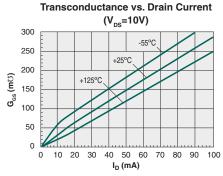

| Forward Transconductance                         | G <sub>FS</sub>           | $I_{D} = 100 \text{mA}, V_{DS} = 10 \text{V}$                       | 225  | -   | -    | m℧             |

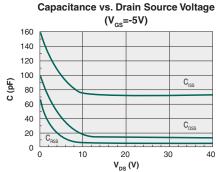

| Input Capacitance                                | C <sub>ISS</sub>          | V <sub>GS</sub> = -5V                                               |      | 70  | 350  |                |

| Common Source Output Capacitance                 | C <sub>OSS</sub>          | V <sub>DS</sub> = 25V                                               | -    | 20  | 60   | pF             |

| Reverse Transfer Capacitance                     | C <sub>RSS</sub>          | f= 1MHz                                                             |      | 10  | 60   |                |

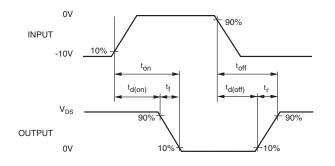

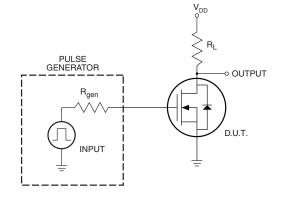

| Turn-On Delay Time                               | t <sub>d(on)</sub>        | V <sub>DD</sub> = 25V                                               |      | 20  |      |                |

| Rise Time                                        | t <sub>r</sub>            | I <sub>D</sub> = 150mA                                              | -    | 10  |      | ns             |

| Turn-Off Delay Time                              | t <sub>d(off)</sub>       | $V_{GS} = 0V \text{ to } -10V$                                      |      | 20  | -    |                |

| Fall time                                        | t <sub>f</sub>            | $R_{gen} = 50\Omega$                                                |      | 50  |      |                |

| Source-Drain Diode Voltage Drop                  | V <sub>SD</sub>           | V <sub>GS</sub> = -5V, I <sub>SD</sub> = 150mA                      | -    | 0.6 | 1.8  | V              |

| Thermal Impedance (Junction to Ambient)          | $\theta_{JA}$             | -                                                                   | -    | 90  | -    | °C/W           |

# **Switching Waveform & Test Circuit**

#### **PERFORMANCE DATA\***

### **Manufacturing Information**

### **Moisture Sensitivity**

All plastic encapsulated semiconductor packages are susceptible to moisture ingression. IXYS Integrated Circuits classifies its plastic encapsulated devices for moisture sensitivity according to the latest version of the joint industry standard, IPC/JEDEC J-STD-020, in force at the time of product evaluation. We test all of our products to the maximum conditions set forth in the standard, and guarantee proper operation of our devices when handled according to the limitations and information in that standard as well as to any limitations set forth in the information or standards referenced below.

Failure to adhere to the warnings or limitations as established by the listed specifications could result in reduced product performance, reduction of operable life, and/or reduction of overall reliability.

This product carries a **Moisture Sensitivity Level (MSL)** classification as shown below, and should be handled according to the requirements of the latest version of the joint industry standard **IPC/JEDEC J-STD-033**.

| Device   | Moisture Sensitivity Level (MSL) Classification |

|----------|-------------------------------------------------|

| CPC3720C | MSL 1                                           |

#### **ESD Sensitivity**

This product is ESD Sensitive, and should be handled according to the industry standard JESD-625.

#### **Soldering Profile**

Provided in the table below is the **IPC/JEDEC J-STD-020** Classification Temperature ( $T_C$ ) and the maximum dwell time the body temperature of these surface mount devices may be ( $T_C$  - 5)°C or greater. The Classification Temperature sets the Maximum Body Temperature allowed for these devices during reflow soldering processes.

| Device   | Classification Temperature (T <sub>c</sub> ) | Dwell Time (t <sub>P</sub> ) | Max Reflow Cycles |

|----------|----------------------------------------------|------------------------------|-------------------|

| CPC3720C | 260°C                                        | 30 seconds                   | 3                 |

#### **Board Wash**

IXYS Integrated Circuits recommends the use of no-clean flux formulations. Board washing to reduce or remove flux residue following the solder reflow process is acceptable provided proper precautions are taken to prevent damage to the device. These precautions include but are not limited to: using a low pressure wash and providing a follow up bake cycle sufficient to remove any moisture trapped within the device due to the washing process. Due to the variability of the wash parameters used to clean the board, determination of the bake temperature and duration necessary to remove the moisture trapped within the package is the responsibility of the user (assembler). Cleaning or drying methods that employ ultrasonic energy may damage the device and should not be used. Additionally, the device must not be exposed to halide flux or solvents.

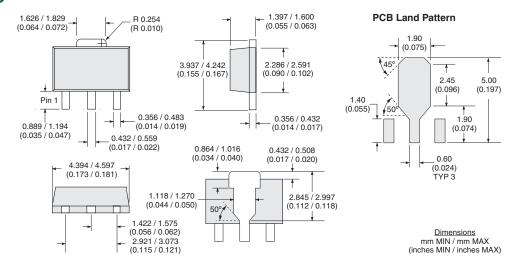

### **MECHANICAL DIMENSIONS**

#### **CPC3720C**

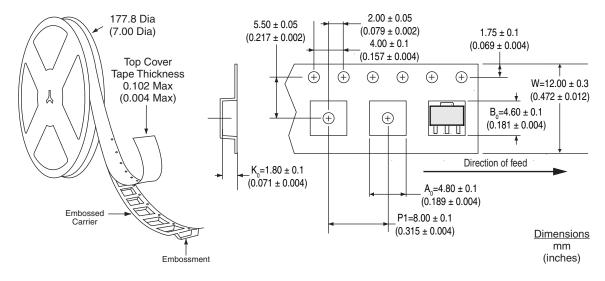

## **CPC3720CTR Tape & Reel**

For additional information please visit our website at: www.ixysic.com

Disclaimer Notice - Information furnished is believed to be accurate and reliable. However, users should independently evaluate the suitability of and test each product selected for their own applications. Littelfuse products are not designed for, and may not be used in, all applications. Read complete Disclaimer Notice at https://www.littelfuse.com/disclaimer-electronics.