#### **Features**

- Drives two N-channel MOSFETs or IGBTs in high-side / low side configuration

- High-side operation up to 600V

- 2.5A source and sink typical output currents

- Outputs tolerant to negative transients

- Wide gate driver supply voltage range: 10V to 20V

- Wide logic input supply voltage range: 3.3V to 20V

- Wide logic supply offset voltage range: -5V to 5V

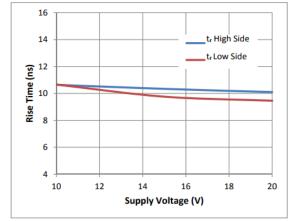

- 15 ns (typical) rise / 13 ns (typical) fall times with 1000 pF load

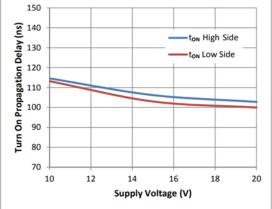

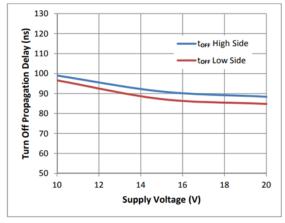

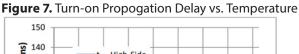

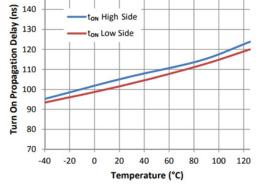

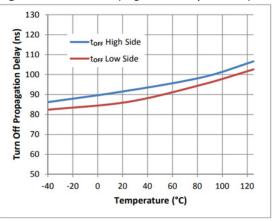

- 105 ns (typical) turn-on / 94 ns (typical) turn-off delay times

- Cycle-by-cycle edge-triggered shutdown circuitry

- Under Voltage Lockout (UVLO) for high and low side drivers

- Extended temperature range: -40 °C to +125 °C

### **Applications**

- DC-DC Converters

- AC-DC Inverters

- Motor Controls

- Class D Power Amplifiers

# LF2110B / LF2113B

High-Side / Low-Side Gate Driver

#### **Description**

The LF2110B and LF2113B are high voltage, high-speed MOSFET and IGBT drivers with independent high-side and low-side outputs. An integrated floating supply enables the high-side driver to operate up to 500V for the LF2110B and up to 600V for the LF2113B. Matched maximum propagation delays of 10ns for the LF2110B and 20ns for the LF2113B allows high frequency operation.

Logic inputs for both LF2110B and LF2113B are compatible with standard CMOS levels (as low as 3.3V) while the driver outputs feature high pulse current buffers designed to minimize driver cross-conduction.

Offered in a 16-lead SOIC package, the LF2110B and LF2113B operate over an extended temperature range of -40 °C to +125 °C.

#### **Ordering Information**

| Part #    | Package | Pack / Qty   | Mark                      |

|-----------|---------|--------------|---------------------------|

| LF2110BTR | SOIC-16 | T & R / 1500 | YYWW<br>LF2110B<br>LOT ID |

| LF2113BTR | SOIC-16 | T & R / 1500 | YYWW<br>LF2113B<br>LOT ID |

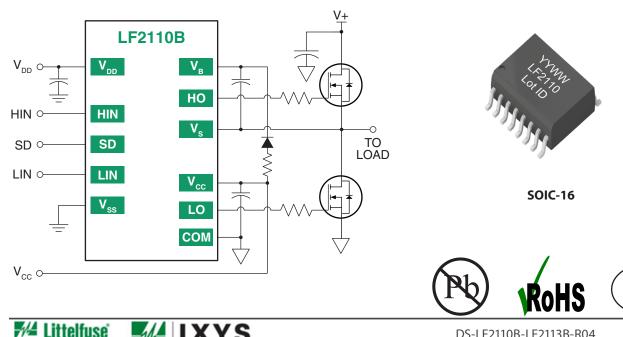

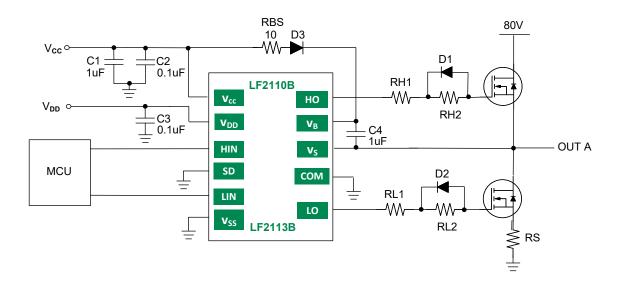

### **Typical Application**

# LF2110B / LF2113B

*High-Side / Low-Side Gate Driver*

### **1** Specifications

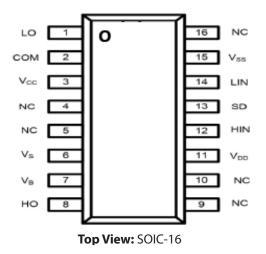

#### 1.1 Pin Diagrams

LF2110B / LF2113B

|                 |                 | i -        |                                                                      |

|-----------------|-----------------|------------|----------------------------------------------------------------------|

| Pin#            | Name            | Туре       | Description                                                          |

| 11              | V <sub>DD</sub> | Power      | Logic positive voltage supply                                        |

| 12              | HIN             | Input      | Logic control for the high-side gate driver output.<br>Non-Inverting |

| 13              | SD              | Input      | Logic control for shutdown                                           |

| 14              | LIN             | Input      | Logic control for the low side gate driver output.<br>Non-Inverting  |

| 15              | V <sub>ss</sub> | Power      | Logic ground                                                         |

| 7               | V <sub>B</sub>  | Power      | High-side gate driver floating positive voltage supply               |

| 8               | НО              | Output     | High-side gate driver output                                         |

| 6               | Vs              | Power      | High-side gate driver floating power supply return                   |

| 3               | V <sub>cc</sub> | Power      | Low-side gate driver positive voltage supply                         |

| 1               | LO              | Output     | Low-side gate driver output                                          |

| 2               | СОМ             | Power      | Low-side gate driver power supply return                             |

| 4, 5, 9, 10, 16 | NC              | No Connect | Not Connected Internally                                             |

#### **1.2 Pin Descriptions**

*High-Side / Low-Side Gate Driver*

Expertise Applied Answers Delivered

#### **1.3 Absolute Maximum Ratings**

| Parameter                                   | Symbol              | Min                  | Мах                  | Units |

|---------------------------------------------|---------------------|----------------------|----------------------|-------|

| High side floating supply voltage (LF2110B) | V <sub>B</sub>      | -0.3                 | +524                 | V     |

| High side floating supply voltage (LF2113B) | V <sub>B</sub>      | -0.3                 | +624                 | V     |

| High side floating supply offset voltage    | V <sub>s</sub>      | V <sub>B</sub> -24   | V <sub>B</sub> +0.3  | V     |

| High side floating output voltage           | V <sub>HO</sub>     | V <sub>s</sub> -0.3  | V <sub>B</sub> +0.3  | V     |

| Offset supply voltage transient             | dV <sub>s</sub> /dt |                      | 50                   | V/ns  |

| Low side fixed supply voltage               | V <sub>cc</sub>     | -0.3                 | +24                  | V     |

| Low side output voltage                     | VLO                 | -0.3                 | V <sub>cc</sub> +0.3 | V     |

| Logic supply voltage                        | V <sub>DD</sub>     | -0.3                 | V <sub>ss</sub> +24  | V     |

| Logic supply offset voltage                 | V <sub>ss</sub>     | V <sub>cc</sub> -24  | V <sub>cc</sub> +0.3 | V     |

| Logic Input voltage (HIN, LIN & SD )        | V <sub>IN</sub>     | V <sub>ss</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| Package power dissipation                   | P <sub>D</sub>      |                      | 1.25                 | W     |

| Junction Temperature                        | T,                  |                      | +150                 | °C    |

| Storage Temperature                         | T <sub>stg</sub>    | -55                  | +150                 | °C    |

Unless otherwise specified all voltages are referenced to COM . All electrical ratings are at  $T_4 = 25 \,^{\circ}\text{C}$

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **1.4 Thermal Characteristics**

| Parameter           | Symbol           | Rating | Units |

|---------------------|------------------|--------|-------|

| Junction to ambient | $\Theta_{_{jA}}$ | 100    | ° C/W |

When mounted on a standard JEDEC 2-layer FR-4 board - JESD51-3

*High-Side / Low-Side Gate Driver*

#### **1.5 Recommended Operating Conditions**

| Parameter                                                             |         | Symbol          | Min                | Мах                 | Unit |

|-----------------------------------------------------------------------|---------|-----------------|--------------------|---------------------|------|

| High side floating supply absolute voltage                            |         | $V_{B}-V_{S}$   | 10                 | 20                  | V    |

| High side floating supply effect voltage                              | LF2110B | V               | Note1              | 500                 | V    |

| High side floating supply offset voltage                              | LF2113B | V <sub>s</sub>  | Note1              | 600                 | V    |

| High side floating output voltage                                     |         | V <sub>HO</sub> | V <sub>s</sub>     | V <sub>B</sub>      | V    |

| Low side fixed supply voltage                                         |         | V <sub>cc</sub> | 10                 | 20                  | V    |

| Low side output voltage                                               |         | V               | 0                  | V <sub>cc</sub>     | V    |

| Logic supply voltage                                                  |         | $V_{\text{DD}}$ | V <sub>ss</sub> +3 | V <sub>ss</sub> +20 | V    |

| Logic supply offset voltage $V_{DD} \ge V_{DD} < V_{DD} < V_{DD} < 0$ |         |                 | -5                 | -                   |      |

|                                                                       |         | V <sub>ss</sub> | - V <sub>DD</sub>  | 5                   | V    |

| Logic Input voltage ( HIN, LIN, SD )                                  |         | V <sub>IN</sub> | V <sub>ss</sub>    | V <sub>DD</sub>     | V    |

| Ambient Temperature                                                   |         | T <sub>A</sub>  | -40                | 125                 | °C   |

Unless otherwise specified all voltages are referenced to COM

**NOTE1** High-side driver remains operational for  $V_s$  transients down to -5V

*High-Side / Low-Side Gate Driver*

Expertise Applied Answers Delivered

#### **1.6 DC Electrical Characteristics**

$V_{CC}=V_{BS}=V_{DD}=15V$ ,  $T_{A}=25$  °C and  $V_{SS}=V_{COM}=0V$ , unless otherwise specified.

The  $V_{\rm M}$  and  $I_{\rm M}$  parameters are applicable to all three logic input pins: HIN, LIN and SD. The  $V_o$  and  $I_o$  parameters are applicable to the respective output pins: HO and LO and are referenced to  $V_{\rm com}$

| Parameter                                                     | Symbol                 | Conditions                                        | Min | Тур | Max  | Unit |

|---------------------------------------------------------------|------------------------|---------------------------------------------------|-----|-----|------|------|

| Logic "1" input voltage                                       | V <sub>IH</sub>        | NOTES                                             | 9.5 |     |      | V    |

| Logic "0" input voltage                                       | V <sub>IL</sub>        | NOTE 2                                            |     |     | 5.0  | V    |

| Logic input voltage hysteresis                                | V <sub>IN(HYS)</sub>   |                                                   |     | 0.3 |      | V    |

| High level output voltage, V <sub>BIAS</sub> - V <sub>O</sub> | V <sub>OH</sub>        | $I_0 = 0A$                                        |     |     | 1.4  | V    |

| Low level output voltage, $V_o$                               | V <sub>OL</sub>        | $I_0 = 20 \text{mA}$                              |     |     | 0.15 | V    |

| Offset supply leakage current<br>LF2110B / LF2113B            | I <sub>LK</sub>        | $V_{B} = V_{S} =$<br>500V/600V                    |     |     | 50   | μΑ   |

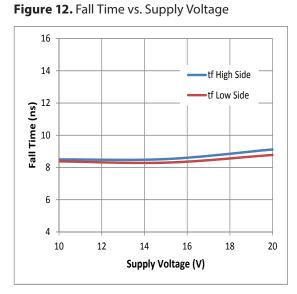

| Quiescent V <sub>BS</sub> supply current                      | I <sub>BSQ</sub>       | $V_{IN} = 0V \text{ or } V_{DD}$                  |     | 55  | 230  | μA   |

| Quiescent V <sub>cc</sub> supply current                      | I <sub>ccq</sub>       | $V_{IN} = 0V \text{ or } V_{DD}$                  |     | 56  | 340  | μA   |

| Quiescent V <sub>DD</sub> supply current                      | I <sub>DDQ</sub>       | $V_{IN} = 0V \text{ or } V_{DD}$                  |     | 0.6 | 30   | μA   |

| Logic "1" input bias current                                  | I <sub>IN+</sub>       | V <sub>IN</sub> = V <sub>DD</sub>                 |     | 20  | 40   | μΑ   |

| Logic "0" input bias current                                  | I <sub>IN-</sub>       | V <sub>IN</sub> =V <sub>SS</sub>                  |     |     | 5.0  | μΑ   |

| V <sub>BS</sub> UVLO off positive going threshold             | $V_{\rm BSUV+}$        |                                                   | 7.5 | 8.6 | 9.7  | V    |

| V <sub>BS</sub> UVLO enable negative going threshold          | V <sub>BSUV-</sub>     |                                                   | 7.0 | 8.2 | 9.4  | V    |

| V <sub>BS</sub> UVLO hysteresis                               | $V_{\text{BSUV(HYS)}}$ |                                                   |     | 0.3 |      | V    |

| V <sub>cc</sub> UVLO off positive going threshold             | $V_{CCUV+}$            |                                                   | 7.4 | 8.5 | 9.6  | V    |

| V <sub>cc</sub> UVLO enable negative going threshold          | V <sub>ccuv-</sub>     |                                                   | 7.0 | 8.2 | 9.4  | V    |

| V <sub>cc</sub> UVLO hysteresis                               | V <sub>ccuv(hys)</sub> |                                                   |     | 0.3 |      | V    |

| Output high short circuit pulsed current                      | I <sub>O+</sub>        | $V_{O} = 0V, V_{IN} = V_{DD'}$ $t \le 10 \ \mu s$ | 2.0 | 2.5 |      | A    |

| Output low short circuit pulsed current                       | I <sub>O-</sub>        | $V_{o} = 15V,$<br>$V_{IN} = 0V, t \le 10 \ \mu s$ | 2.0 | 2.5 |      | A    |

**NOTE 2** For optimal operation, it is recommended the input pulse (to HIN and LIN) should have a minimum amplitude of 9.5V ( $V_{DD}$ =15V) with a minimum pulse width of 200ns.

*High-Side / Low-Side Gate Driver*

Expertise Applied Answers Delivered

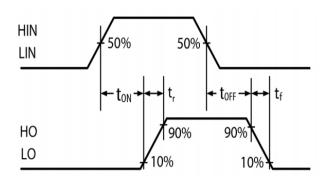

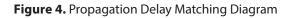

#### **1.7 AC Electrical Characteristics**

$V_{CC} = V_{BS} = V_{DD} = 15V$ ,  $T_A = 25$  °C,  $C_L = 1000$  pF, and  $V_{SS} = V_{COM} = 0V$  unless otherwise specified.

| Parameter                   | Symbol           | Conditions                    | Min | Тур | Max | Unit |

|-----------------------------|------------------|-------------------------------|-----|-----|-----|------|

| Turn-on propagation delay   | t <sub>on</sub>  | $V_s = 0V$                    |     | 105 | 150 | ns   |

|                             |                  | LF2110B: V <sub>s</sub> =500V |     | 94  | 125 |      |

| Turn-off propagation delay  | t <sub>off</sub> | LF2113B: V <sub>s</sub> =600V |     |     |     | ns   |

|                             | t <sub>sD</sub>  | LF2110B: V <sub>s</sub> =500V |     | 70  | 140 |      |

| Shut down propagation delay |                  | LF2113B: V <sub>s</sub> =600V |     |     |     | ns   |

| Turn-on rise time           | t,               |                               |     | 15  | 35  | ns   |

| Turn-off fall time          | t <sub>f</sub>   |                               |     | 13  | 25  | ns   |

| Propagation Delay Matching  | t <sub>DM</sub>  | LF2110B                       |     |     | 10  | ns   |

|                             |                  | LF2113B                       |     |     | 20  | ns   |

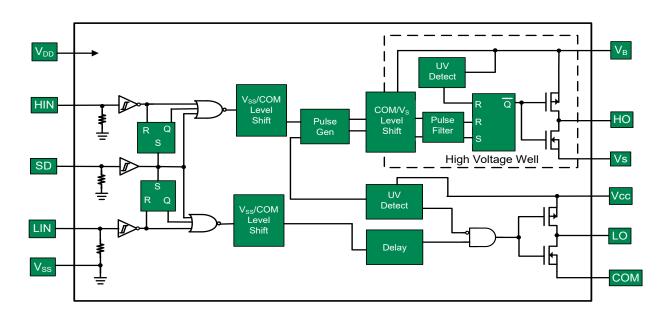

### **2** Functional Description

#### 2.1 Functional Block Diagram

*High-Side / Low-Side Gate Driver*

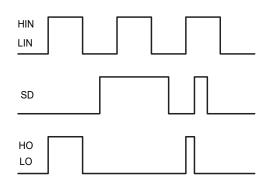

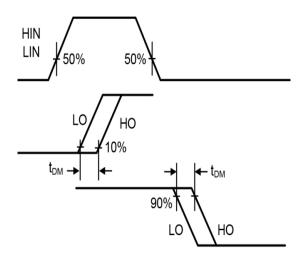

#### 2.2 Timing Waveforms

Figure 1. Input / Output Logic Diagram

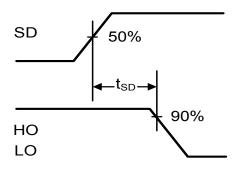

Figure 3. Shutdown Timing Diagram

Figure 2. Input-to-Output Delay Timing Diagram

High-Side / Low-Side Gate Driver

#### **2.3 Application Information**

**Figure 5.** Single phase (of four) for Stepper motor driver application using the LF2110B / LF2113B

**R**H1 and RL1 value is typically between  $5\Omega$  and  $10\Omega$ , exact value decided by MOSFET junction capacitance and drive current of gate driver;  $10\Omega$  is used in this example.

■ It is **highly recommended** that the input pulse (to HIN and LIN) should have a minimum amplitude of 9.5V (for VDD=15V) with a minimum pulse width of 200ns.

**RH2** and RL2 value is typically between  $20\Omega$  and  $100\Omega$ , exact value decided by MOSFET junction capacitance and drive current of gate driver;  $50\Omega$  is used in this example.

D3 is rated at 1000V, 1A. Use Diodes Inc. US1M or equivalent .

High-Side / Low-Side Gate Driver

Expertise Applied Answers Delivered

#### **3 Performance Data**

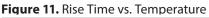

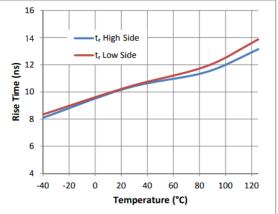

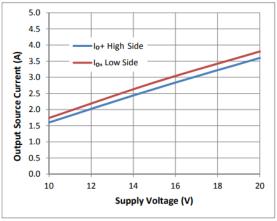

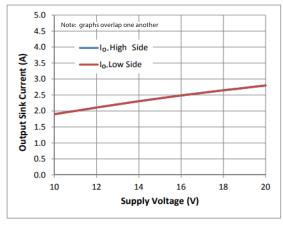

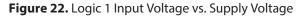

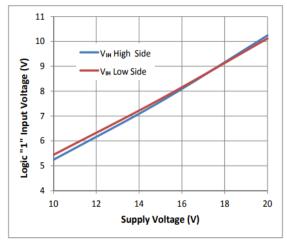

Unless otherwise noted  $V_{CC} = V_{BS} = V_{DD} = 12V$ ,  $T_A = 25$  °C,  $V_{SS} = V_{COM} = 0V$  and values are typical.

Figure 8. Turn-off Propogation Delay vs. Supply Voltage

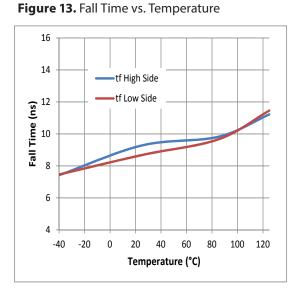

#### Figure 9. Turn-off Propogation Delay vs. Temperature

# LF2110B / LF2113B

High-Side / Low-Side Gate Driver

Figure 14. Quiescent Current vs. Supply Voltage

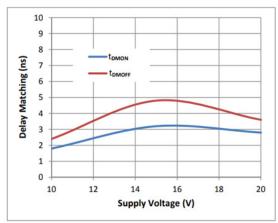

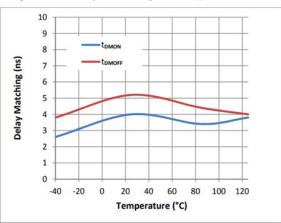

Figure 16. Delay Matching vs. Supply Voltage

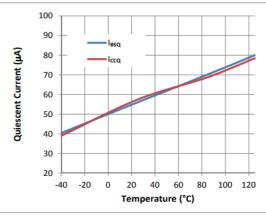

Figure 15. Quiescent Current vs. Temperature

Figure 17. Delay Matching vs. Temperature

# LF2110B / LF2113B

High-Side / Low-Side Gate Driver

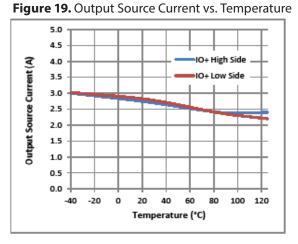

Figure 18. Output Source Current vs. Supply Voltage

#### Figure 20. Output Sink Current vs. Supply Voltage

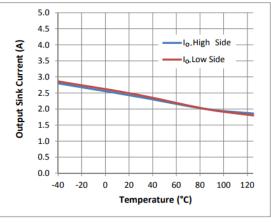

#### Figure 21. Output Sink Current vs. Temperature

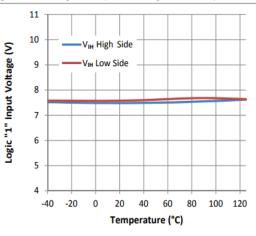

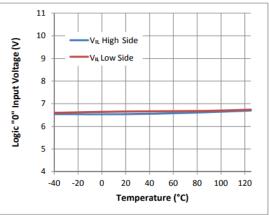

Figure 23. Logic 1 Input Voltage vs. Temperature

**LF2110B / LF2113B**

High-Side / Low-Side Gate Driver

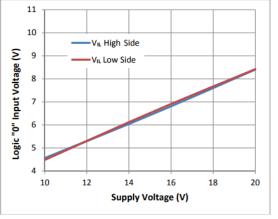

Figure 24. Logic 0 Input Voltage vs. Supply Voltage

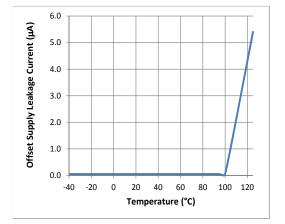

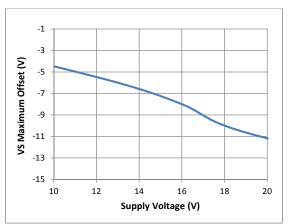

Figure 28. Offset Supply Leakage Current vs. Temperature Figure 29. V<sub>s</sub> Maximum Offset vs. Supply Voltage

Figure 25. Logic 0 Input Voltage vs. Temperature

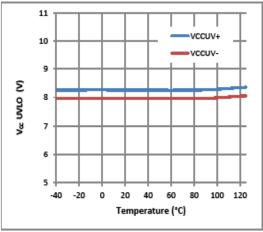

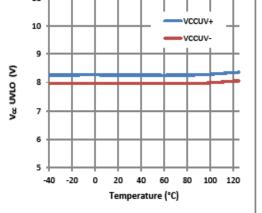

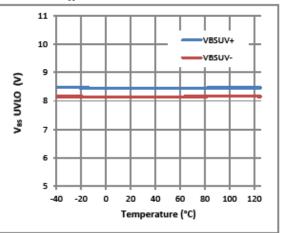

#### Figure 27. V<sub>BS</sub> UVLO vs. Temperature

*High-Side / Low-Side Gate Driver*

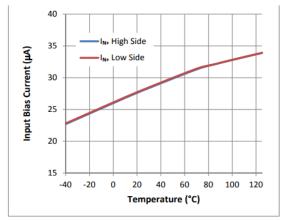

Figure 30. Input Bias Current vs. Temperature

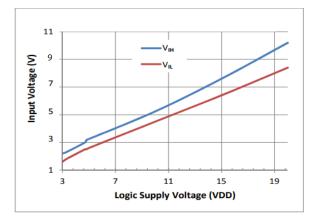

#### Figure 31. Input Voltage Threshold vs. $V_{_{DD}}$

High-Side / Low-Side Gate Driver

Expertise Applied Answers Delivered

#### 4 Manufacturing Information

#### 4.1 Moisture Sensitivity

All plastic encapsulated semiconductor packages are susceptible to moisture ingression. Littelfuse Integrated Circuits Division classified all of its plastic encapsulated devices for moisture sensitivity according to the latest version of the joint industry standard, **IPC/JEDEC J-STD-020**, in force at the time of product evaluation. We test all of our products to the maximum conditions set forth in the standard, and guarantee proper operation of our devices when handled according to the limitations and information in that standard as well as to any limitations set forth in the information or standards referenced below.

Failure to adhere to the warnings or limitations as established by the listed specifications could result in reduced product performance, reduction of operable life, and/or reduction of overall reliability.

This product carries a **Moisture Sensitivity Level (MSL)** rating as shown below, and should be handled according to the requirements of the latest version of the joint industry standard **IPC/JEDEC J-STD-033**.

| Device           | Moisture Sensitivity Level (MSL)<br>Classification |  |

|------------------|----------------------------------------------------|--|

| LF2110B, LF2113B | MSL3                                               |  |

#### 4.2 ESD Sensitivity

This product is **ESD Sensitive**, and should be handled according to the industry standard **JESD-625**.

#### **4.3 Reflow Profile**

Provided in the table below is the IPC/JEDEC J-STD-020 Classification Temperature ( $T_c$ ) and the maximum dwell time the body temperature of these surface mount devices may be ( $T_c$  - 5)°C or greater. The Classification Temperature sets the Maximum Body Temperature allowed for these devices during reflow soldering processes.

| Device           | Classification<br>Temperature(Tc) | Dwell Time (tp) | Max<br>Reflow Cycles |  |

|------------------|-----------------------------------|-----------------|----------------------|--|

| LF2110B, LF2113B | 260°C                             | 30 seconds      | 3                    |  |

High-Side / Low-Side Gate Driver

#### 4.4 Board Wash

Littelfuse recommends the use of no-clean flux formulations. Board washing to reduce or remove flux residue following the solder reflow process is acceptable provided proper precautions are taken to prevent damage to the device. These precautions include but are not limited to: using a low pressure wash and providing a follow up bake cycle sufficient to remove any moisture trapped within the device due to the washing process. Due to the variability of the wash parameters used to clean the board, determination of the bake temperature and duration necessary to remove the moisture trapped within the package is the responsibility of the user (assembler). Cleaning or drying methods that employ ultrasonic energy may damage the device and should not be used. Additionally, the device must not be exposed to halide flux or solvents.

High-Side / Low-Side Gate Driver

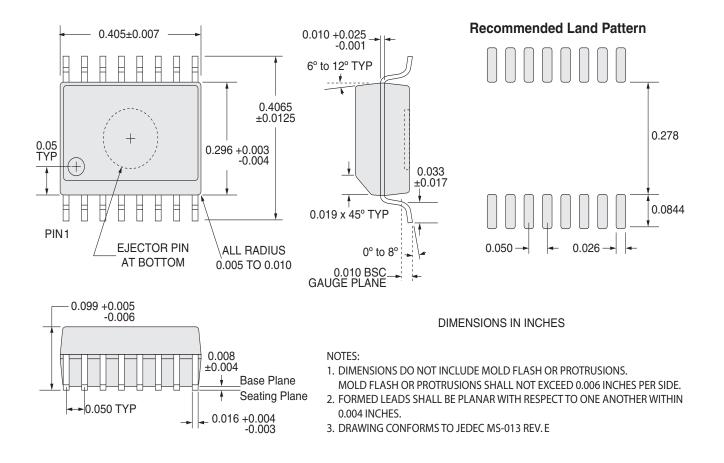

### 5 Package Dimensions (SOIC-16)

#### **Important Notice**

Disclaimer Notice - Information furnished is believed to be accurate and reliable. However, users should independently evaluate the suitability of and test each product selected for their own applications. Littelfuse products are not designed for, and may not be used in, all applications. Read complete Disclaimer Notice at https://www.littelfuse.com/disclaimer-electronics.

Specification: DS-LF2110B-LF2113B-R04 ©Copyright 2022, Littelfuse, Inc. All rights reserved. Printed in USA. 3/17/2022